## COMPUTING COMPUT

- High Performance Computing

- Memory

- Careers

- Low Code

**IEEE Computer Society**

# Grants for EMERGING TECHNOLOGY ACTIVITIES

MAKE AN IMPACT | CREATE SOLUTIONS

Are you connecting the computing community with emerging technologies? Help advance emerging tech to create solutions for the betterment of humanity.

Every year, we give up to \$50,000 in funding per project for these efforts.

Learn more at

computer.org/communities/emerging-technology-fund

#### IEEE COMPUTER SOCIETY computer.org

#### **STAFF**

**Editor** Lucy Holden

**Production & Design Artist**Carmen Flores-Garvey

**Periodicals Portfolio Senior Managers** Carrie Clark and Kimberly Sperka

**Periodicals Operations Project Specialists**Priscilla An and Christine Shaughnessy

**Director, Periodicals and Special Projects**Robin Baldwin

**Senior Advertising Coordinator**Debbie Sims

Circulation: ComputingEdge (ISSN 2469-7087) is published monthly by the IEEE Computer Society. IEEE Headquarters, Three Park Avenue, 17th Floor, New York, NY 10016-5997; IEEE Computer Society Publications Office, 10662 Los Vaqueros Circle, Los Alamitos, CA 90720; voice +1 714 821 8380; fax +1 714 821 4010; IEEE Computer Society Headquarters, 2001 L Street NW, Suite 700, Washington, DC 20036.

**Postmaster:** Send address changes to *ComputingEdge*-IEEE Membership Processing Dept., 445 Hoes Lane, Piscataway, NJ 08855. Periodicals Postage Paid at New York, New York, and at additional mailing offices. Printed in USA.

**Editorial:** Unless otherwise stated, bylined articles, as well as product and service descriptions, reflect the author's or firm's opinion. Inclusion in *ComputingEdge* does not necessarily constitute endorsement by the IEEE or the Computer Society. All submissions are subject to editing for style, clarity, and space.

Reuse Rights and Reprint Permissions: Educational or personal use of this material is permitted without fee, provided such use: 1) is not made for profit; 2) includes this notice and a full citation to the original work on the first page of the copy; and 3) does not imply IEEE endorsement of any third-party products or services. Authors and their companies are permitted to post the accepted version of IEEE-copyrighted material on their own Web servers without permission, provided that the IEEE copyright notice and a full citation to the original work appear on the first screen of the posted copy. An accepted manuscript is a version which has been revised by the author to incorporate review suggestions, but not the published version with copyediting, proofreading, and formatting added by IEEE. For more information, please go to: http://www.ieee.org/publications\_standards/publications/rights/paperversionpolicy.html. Permission to reprint/republish this material for commercial, advertising, or promotional purposes or for creating new collective works for resale or redistribution must be obtained from IEEE by writing to the IEEE Intellectual Property Rights Office, 445 Hoes Lane, Piscataway, NJ 08854-4141 or pubs-permissions@ieee.org. Copyright © 2025 IEEE. All rights reserved.

**Abstracting and Library Use:** Abstracting is permitted with credit to the source. Libraries are permitted to photocopy for private use of patrons, provided the per-copy fee indicated in the code at the bottom of the first page is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923.

**Unsubscribe:** If you no longer wish to receive this *ComputingEdge* mailing, please email IEEE Computer Society Customer Service at help@computer.org and type "unsubscribe *ComputingEdge*" in your subject line.

IEEE prohibits discrimination, harassment, and bullying. For more information, visit www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### 2025 IEEE Computer Society Magazine Editors in Chief

#### Computer

Jeff Voas, NIST

#### Computing in Science & Engineering

Jeffrey Carver, University of Alabama

#### IEEE Annals of the History of Computing

Troy Astarte, Swansea University

#### IEEE Computer Graphics and Applications

Pak Chung Wong, Trovares and Bill & Melinda Gates Foundation (Interim EIC)

#### **IEEE Intelligent Systems**

Bo An, Nanyang Technological University

#### **IEEE Internet Computing**

Weisong Shi, *University of Delaware*

#### **IEEE Micro**

Hsien-Hsin Sean Lee, Intel Corporation

#### IEEE MultiMedia

Balakrishnan Prabhakaran, University of Texas at Dallas

#### **IEEE Pervasive Computing**

Fahim Kawsar, Nokia Bell Labs and University of Glasgow

#### **IEEE Security & Privacy**

Sean Peisert, Lawrence Berkeley National Laboratory and University of California, Davis

#### **IEEE Software**

Sigrid Eldh, Ericsson, Mälardalen University, Sweden; Carleton University, Canada

#### **IT Professional**

Charalampos Z. Patrikakis, *University of West Attica*

Building a Diverse and Inclusive HPC Community for Mission-Driven Team Science 16

Predicting the Future of Supercomputing 36

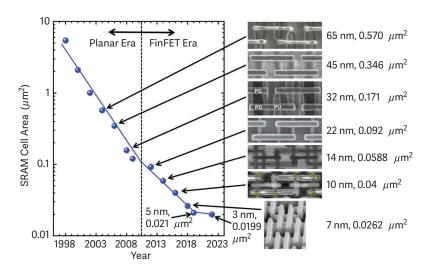

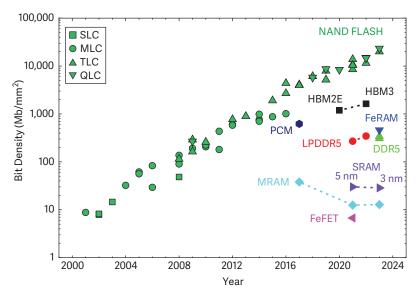

Semiconductor Memory Technologies: State-of-the-Art and Future Trends

8 Building a Diverse and Inclusive HPC Community for Mission-Driven Team Science

LOIS CURFMAN MCINNES, PAIGE KINSLEY, MARY ANN LEUNG, DANIEL MARTIN, SUZANNE PARETE-KOON, AND SREERANJANI JINI RAMPRAKASH

16 Predicting the Future of Supercomputing

SCOTT ATCHLEY, ROSA M. BADIA, BRONIS R. DE SUPINSKI, JOSHUA FRYMAN, DIETER KRANZLMÜLLER, SRILATHA MANNE, PEKKA MANNINEN, SATOSHI MATSUOKA, DEJAN MILOJICIC, GALEN SHIPMAN, ERIC VAN HENSBERGEN, AND ROBERT W. WISNIEWSKI

#### **Memory**

30 How Emerging Memories Extend Battery Life

JIM HANDY AND TOM COUGHLIN

36 Semiconductor Memory Technologies: State-of-the-Art and Future Trends

SHIMENG YU AND TAE-HYEON KIM

#### **Careers**

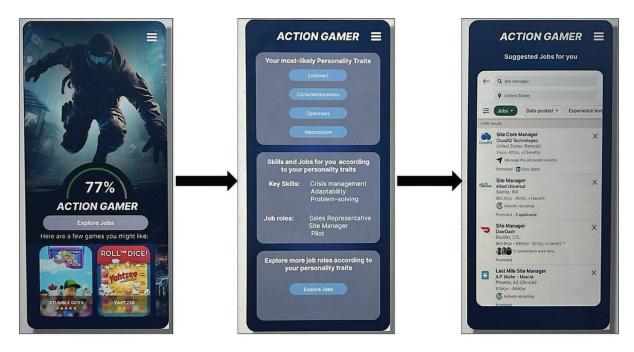

42 How to Hire a Gen Z Through Gaming

KHIZER KHADERI, YUSUF AHMED, AND MICHAEL ZYDA

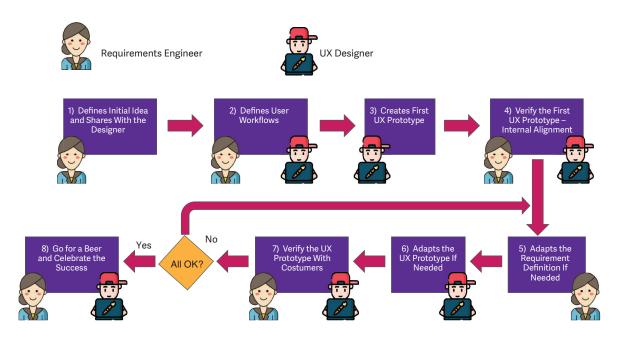

52 My REvelation: Unveiling an Unseen Career in Requirements

SOFIJA HOTOMSKI

#### **Low Code**

56 Citizen Development, Low-Code/No-Code Platforms, and the Evolution of Generative AI in Software Development

J. T. SODANO AND JOANNA F. DEFRANCO

#### **Departments**

- 4 Magazine Roundup

- 7 Editor's Note: The Future of High-Performance Computing

- 64 Conference Calendar

Subscribe to *ComputingEdge* for free at www.computer.org/computingedge

## Magazine Roundup

he IEEE Computer Society's lineup of 12 peer-reviewed technical magazines covers cutting-edge topics ranging from software design and computer graphics to Internet computing and security, from scientific applications and machine intelligence to visualization and microchip design. Here are highlights from recent issues.

#### Computer

Envisioning the Next-Generation Cellular Architecture With Named Data Networking

This article, featured in the August 2025 issue of *Computer*, proposes adopting named data networking (NDN) as a foundation for future cellular networks, including 6G, to shift the focus from connection-based to data-centric communication. Securing data at the network layer, NDN reduces control plane signaling overhead and enables secure distributed deployments.

#### computing

Adaptive Computing for Scale-Up Problems

Adaptive computing is an application-agnostic outer-loop framework to strategically deploy simulations and experiments to guide decision making for scale-up analysis. The framework enables the characterization and management of uncertainties associated with predictive models of complex systems when scale-up questions lead to significant model extrapolation. This January–March 2025

Computing in Science & Engineering article discusses applications of this framework to problems in the renewable energy space, including biofuels production, material synthesis, perovskite crystal growth, and building electrical loads.

Operation Voder: AT&T, Bell Labs, and the Labor of Techno-Utopia at the 1939 New York World's Fair

This article, featured in the April-June 2025 issue of IEEE Annals of the History of Computing, explores the labor demands of the Voder, the electrical speech synthesis machine developed by Bell Labs for AT&T's 1939 New York World's Fair exhibit. The author argues that AT&T executives used Voder operators to normalize a new vision of technological utopia that relied heavily and conspicuously on the infrastructural labor of women. Moreover, the article highlights the previously unacknowledged engineering contributions of Voder operators in the years before the fair, writing women into the origin story of a machine that

laid critical groundwork for speech recognition and voice encryption technology.

#### Computer Graphics

What Data Do and Do Not Represent: Visualizing the Archive of Slavery

The authors of this article, featured in the May/June 2025 issue of IEEE Computer Graphics and Applications, present a design report on a humanistically informed data visualization of a dataset related to the trans-Atlantic slave trade. The visualization employs a quantitative dataset of slaving voyages that took place between 1565 and 1858 and uses historical scholarship and humanistic theory to call attention to the people behind the data, as well as to what the data do not or cannot represent.

#### lintelligent Systems

Wet-Neuromorphic Computing: A New Paradigm for Biological Artificial Intelligence

As we delve into a life governed by artificial intelligence (AI), ongoing

research continues to discover new forms of intelligence that are efficient and closely mimic an organism's brain in terms of performance. This article, which was in the May/ June 2025 issue of *IEEE Intelligent Systems*, presents a new concept termed wet-neuromorphic computing, in which biological cells or organisms are leveraged to perform computational tasks using their natural molecular functions.

#### **Internet Computing**

#### Toward Carbon-Aware Data Transfers

The growing adoption of cloud, edge, and distributed computing, as well as the rise in the use of artificial intelligence/machine learning workloads, have created a significant need to measure, monitor, and reduce the carbon emissions associated with these resourceintensive tasks. One significant but often overlooked source of emissions is data transfers over widearea networks, primarily due to the challenges in accurately measuring the carbon footprint of endto-end network paths. The authors of this article from the March/April 2025 issue of IEEE Internet Computing introduce a novel mechanism to measure network carbon footprints and propose strategies for optimizing the scheduling of network-intensive tasks.

#### The IBM Telum II Processor

This article, featured in the May/ June 2025 issue of IEEE Micro, presents IBM Telum II, the latest processor designed specifically for IBM Z's next-generation mainframe. Designed-for-purpose, Telum II is focused on mission-critical enterprise workloads where performance and sustainability are of the utmost importance and the demand for artificial intelligence acceleration is increasing dramatically. Innovations discussed in this article are the new on-die data processing unit for input/output acceleration, the updated cache, enhancements to the on-chip artificial intelligence accelerator, core improvements, and changes to the off-chip input/ output interfaces.

#### **MultiMedia**

#### A Novel Hybrid Epidemic Prediction Model Based on Cross-Modal Information

To assess the threat of the COVID-19 epidemic, forecasting the number of new cases is critical for epidemic prevention. The authors of this January–March 2025 *IEEE MultiMedia* article propose a novel cross-modal spatial-temporal epidemic prediction (CMSTEP) model

for COVID-19 new-case prediction. The proposed model consists of two newly designed modules: one is a spatial-temporal sequential prediction module that captures the trend of new cases based on the historical epidemic of the target region and its related regions, the other is an intervention effect assessment module that models the NPIs' impact based on their orientations and effective durations.

#### Data-Driven Adaptation of Smart Grids With Hierarchical Digital Twins

Local energy communities are citizens' associations that allow efficient energy sharing and management among their members. Such organizations play a crucial role in the energy transition, and smart grids represent the core technology for their implementation. In this January-March 2025 IEEE Pervasive Computing article, the authors propose a framework based on hierarchical Digital Twins interconnecting the physical devices of the smart grid. By exploiting this framework, they propose an energy-sharing approach in which users of a local energy community can share the excess local batteries' capacity with each other.

#### SECURITY& PRIVACY

Trajectories of Piracy and Cyberbullying Across Adolescence

This article, featured in the May/ June 2025 issue of *IEEE Security & Privacy*, investigates the pathways and predictors of piracy and cyberbullying among Korean adolescents using longitudinal data from 2003–2008. Findings reveal distinct trajectories and predictors for each behavior. This highlights the need for targeted interventions and challenges existing international cybercrime policies.

challenges, particularly with the rise of false base station (FBS) attacks. This article, featured in the May/June 2025 issue of IT Professional, investigates the vulnerabilities of 5G networks exploited by FBSs, which hijack communications by mimicking legitimate base stations and compromising user equipment (UE). This research provides critical insights into securing 5G networks, emphasizing the importance of adaptive defense strategies against evolving cyber threats.

#### Söftware

From Code Generation to Software Testing: AI Copilot With Context-Based Retrieval-Augmented Generation

The rapid pace of large-scale soft-ware development places increasing demands on traditional testing methodologies. This article from the July/August 2025 issue of *IEEE Software* proposes a novel perspective on software testing, highlighting the transformative potential of Al-driven technologies in modern software development practices.

#### **Professional**

Exposing and Addressing Fake Base Station Vulnerabilities in 5G Through User Device Exploits

The rapid advancement of 5G networks introduces new security

#### **IEEE**DataPort **STORE, SEARCH & MANAGE** RESEARCH DATA Individual subscriptions to IEEE DataPort are free for all IEEE society members and Young Professionals. Just log in and activate your subscription for unlimited access to datasets, data management tools, dataset storage for your own research, and more. **Open Access** 2 TB of Cloud Link to **Options** Storage **Manuscripts** Reproducible **Citations** Research **Host Data** Competitions

#### The Future of High-Performance Computing

upercomputing, a type of high-performance computing (HPC), will continue to evolve over the next decade to meet the need of rising artificial intelligence/machine learning (AI/ML) use. The HPC field must adapt and grow, which includes expanding and diversifying its workforce. This issue of ComputingEdge discusses initiatives to bring diversity and inclusivity into HPC as well as the outlook of supercomputing, including increasing uses and adoption. The articles also explore new advancements in battery and semiconductor memory, and delve into careers in requirements engineering (RE) and video game career recruitment. The issue concludes with a discussion of developments in low-code/nocode (LCNC) platforms.

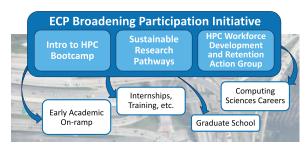

There is much on the horizon for supercomputing, from developments in AI/ML techniques to improving representation in the workforce by key communities. Computing in Science & Engineering article "Building a Diverse and Inclusive HPC Community for Mission-Driven Team Science" presents strategies aimed at increasing and diversifying the HPC workforce through bootcamps, internships, and a workforce development and retention group. The authors of "Predicting the Future of Supercomputing" from Computer, address the needs, challenges, and opportunities for supercomputing over the next decade.

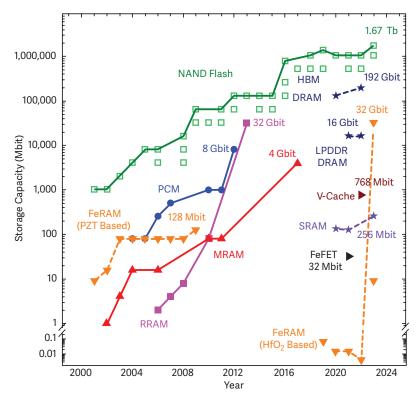

The explosion of Internet of Things (IoT) devices and data-intensive applications in AI and ML is straining current memory supply and capacity. In *Computer* article "How Emerging Memories Extend Battery Life," the authors explore new nonvolatile memory types, which can help balance the tradeoffs between functionality, portability, and battery life in IoT devices. In "Semiconductor Memory

Technologies: State-of-the-Art and Future Trends" from *Computer*, the authors survey the recent development of semiconductor memory technologies, which can improve capacity and speed.

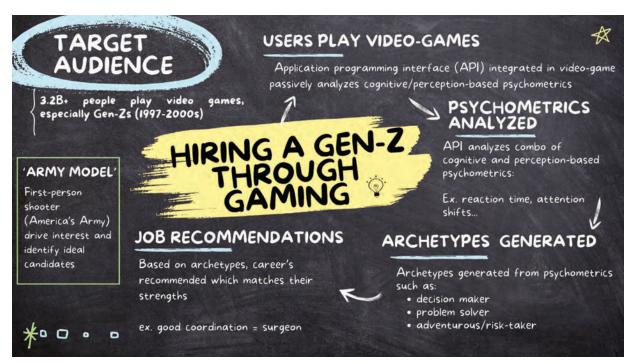

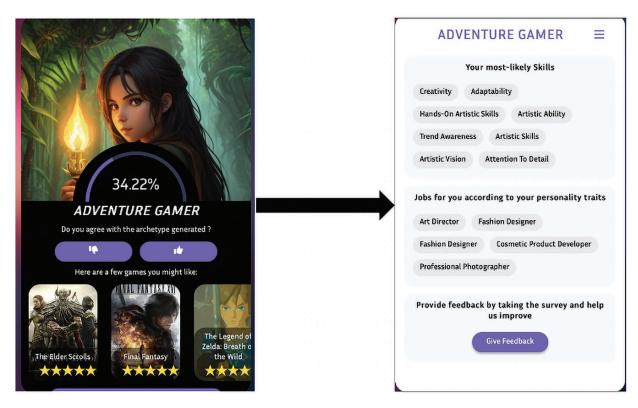

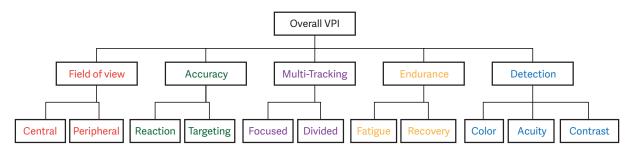

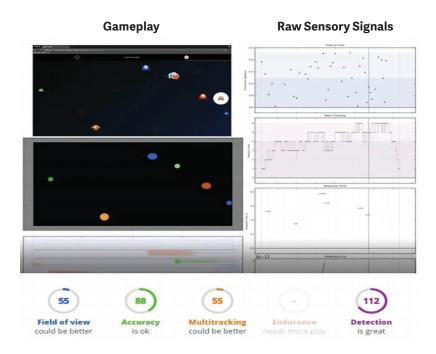

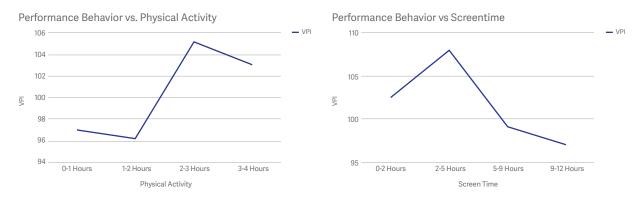

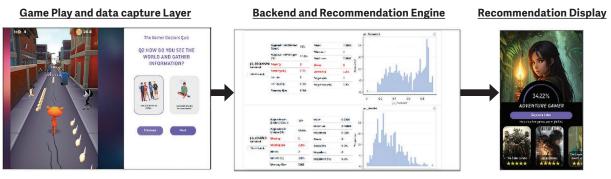

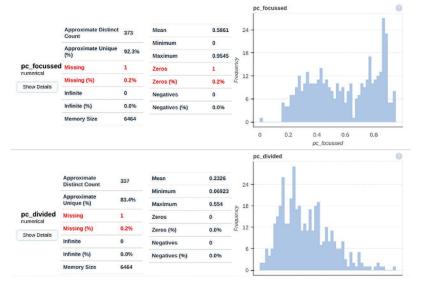

Unusual career routes can lead to careers in RE, and video games can be a tool in career recruitment to attract the Gen Z workforce. Computer article "How to Hire a Gen Z Through Gaming" outlines a strategy for how to use any game as a recruiting tool for Gen Z. In IEEE Software article "My REvelation: Unveiling an Unseen Career in Requirements," the author explains how she found a career in RE.

The authors of "Citizen Development, Low-Code/No-Code Platforms, and the Evolution of Generative Al in Software Development," from *Computer*, show how an increased use of LCNC platforms combined with Al can help supplement the shortage of software developers and engineers.

#### DEPARTMENT: DIVERSITY AND INCLUSION

## Building a Diverse and Inclusive HPC Community for Mission-Driven Team Science

Lois Curfman McInnes and Paige Kinsley, Argonne National Laboratory, Lemont, IL, 60439, USA Mary Ann Leung, Sustainable Horizons Institute, Rancho Mirage, CA, 92270, USA Daniel Martin, Lawrence Berkeley National Laboratory, Berkeley, CA, 94720, USA Suzanne Parete-Koon, Oak Ridge National Laboratory, Oak Ridge, TN, 37831, USA Sreeranjani (Jini) Ramprakash, Argonne National Laboratory, Lemont, IL, 60439, USA

The U.S. Department of Energy (DOE) has been a long-standing leader in driving advances in science and technology through advanced computing. However, DOE laboratories are currently facing urgent workforce challenges, particularly in terms of underrepresentation from key communities, including people of color, women, persons with disabilities, and first-generation scholars. This paper introduces the work carried out as part of the Exascale Computing Project (ECP) Broadening Participation Initiative, which aims to address workforce challenges through a lens that considers the distinct needs and culture of high-performance computing (HPC). The work focuses on three main efforts: hosting Intro to HPC Bootcamps, expanding the Sustainable Research Pathways (SRP) internship and workforce development program, and establishing an HPC Workforce Development and Retention Action Group. The paper also highlights various workforce efforts throughout the computational science community and explores opportunities for future work aimed at broadening participation in HPC.

he U.S. Department of Energy (DOE) is a long-standing leader in scientific discovery enabled through high-performance computing (HPC). Associated with 118 Nobel Prize winners, the 17 DOE national laboratories conduct a wide array of basic and applied science research, with emphasis on solving big problems through mission-driven team science. DOE's investments have pushed the growth of computational and data-enabled science and engineering as a foundation of scientific and technological progress in conjunction with theory and experimentation. Computational science—at the intersection of mathematics and statistics, computer science, and core disciplines of science and engineering—is revolutionizing not only the traditional physical sciences, but also life sciences, social

sciences, humanities, business, finance, and even government policy.

#### BUILDING THE WORKFORCE TO TACKLE BIG PROBLEMS THROUGH HPC TEAM SCIENCE

As we tackle next-generation challenges and problems otherwise intractable—bridging scales and domains through new multiscale and multiphysics algorithms that exploit advanced computing architectures, incorporating complex workflows that couple modeling/simulation and experimental/observational data, leveraging artificial intelligence/machine learning (AI/ML) tools for enhanced insight, and working toward greater scientific reproducibility—we face a new era of complexity.

Past success has relied on developing a highly inter- and multidisciplinary workforce and culture that fosters cross-disciplinary communication and not only exploits but also celebrates the unique expertise of

1521-9615 © 2024 IEEE Digital Object Identifier 10.1109/MCSE.2023.3348943 Date of current version 12 April 2024. each field. The combined expertise of diverse teams is increasingly essential, including applied mathematicians, computer scientists, domain scientists, and research software engineers,<sup>a</sup> along with project coordinators, social scientists, and more.<sup>2</sup> Moreover, various studies have shown that diverse organizations and groups are more creative, innovative, and productive.<sup>3,4</sup>

#### **HPC Workforce Challenges**

DOE national laboratories, like many other scientific research organizations, face growing needs and challenges in recruiting and retaining a skilled workforce in the computing sciences.<sup>5</sup> HPC has additional constraints stemming from its reliance on a workforce versed not only in advanced computing but also in multi- and interdisciplinary science and engineering domains, which also face challenges in recruiting and retaining underrepresented populations.<sup>b</sup> Government and academic sectors face fierce competition for talent attracted to lucrative industrial workplace benefits. Moreover, the changing U.S. demographics and higher attrition rates among people from underrepresented groups present additional challenges.

Cultivating the HPC workforce appears to be an over-constrained problem: growing needs, higher competition, changing workforce demographic profiles, and higher attrition rates in demographic groups currently underrepresented in HPC, but growing in the general workforce population. Moreover, while HPC has successfully cultivated a technically diverse workforce and many successful recruitment models exist, widespread reliance on existing social and professional networks has largely resulted in a homogeneous workforce. The challenge is not only to develop new approaches to broaden the reach but also to change longstanding recruitment, onboarding, and retention practices to create and sustain an inclusive and diverse HPC workforce.

#### Advancing the HPC Workforce

Addressing these workforce challenges requires broad community collaboration to change the culture and

ahttps://us-rse.org, https://society-rse.org

demographic profile of computational science. Impactful DOE-wide programs such as SULI, d GEM, e VFP, f CCI,g and activitiesh in the wider computing community<sup>7,8</sup> are making headway. Likewise, events such as Advanced Computing for Social Change,<sup>9</sup> The Pipeline Workshop, and Scaling HPC Education are pioneering innovative formats to engage underrepresented students in HPC. In addition, various communities are exploring strategies to improve HPC education and training; for example, a working group<sup>10</sup> made recommendations for overcoming key challenges in undergraduate-level education in computing and HPC, including building an HPC educator community and developing and providing inexpensive HPC hardware as teaching tools. Meanwhile, laboratory-specific initiatives are addressing challenges in workforce and training, capitalizing on each lab's unique perspectives, culture, and regional connections to underrepresented populations.

#### ECP BROADENING PARTICIPATION INITIATIVE

The DOE Exascale Computing Project (ECP)<sup>k</sup> is a research, development, and deployment project spanning multiple national labs as well as academic and private institutions. Beginning in 2016, ECP has engaged 1000 researchers over seven years on the development of an integrated scientific computing software stack for use on exascale supercomputers (capable of executing 10<sup>18</sup> operations per second) and the demonstration of new and faster capabilities in a wide variety of applications in chemistry, materials, energy, Earth and space sciences, data analytics, optimization, AI, and

<sup>d</sup>DOE Science Undergraduate Laboratory Internships (SULI, https://science.osti.gov/wdts/suli) encourage undergraduate students to pursue STEM careers by providing research experiences at DOE laboratories.

eThe GEM Fellowship Program (https://gemfellowship.org) seeks to recruit high-quality underrepresented students looking to pursue degrees in applied science and engineering.

The DOE Visiting Faculty Program, (VFP, https://science.osti.gov/wdts/vfp) seeks to increase the research competitiveness of faculty members and their students at institutions historically underrepresented in the research community. The DOE Community College Internships Program (CCI, https://science.osti.gov/wdts/cci) seeks to encourage community college students to enter technical careers relevant to the DOE mission.

<sup>h</sup>Best Practices for Diversity and Inclusion in STEM Education and Research: A Guide by and for Federal Agencies, National Science and Technology Council, https://www.whitehouse.gov/wp-content/uploads/2021/09/091621-Best-Practices-for-Diversity-Inclusion-in-STEM.pdf.

https://cra.org/cra-wp/events/pipeline-workshop-diversifyinghpc-workforce/

jhttps://supercloud.mit.edu/scaling-hpc-education

khttps://exascaleproject.org

<sup>&</sup>lt;sup>b</sup>As discussed in a 2023 NSF report, https://ncses.nsf.gov/pubs/nsf23315/, women and racial and ethnic minorities are underrepresented in U.S. science and engineering programs.

<sup>&</sup>lt;sup>c</sup>Demographic data for DOE national laboratories provides workforce insights, https://nationallabs.org/staff/diversity. According to a 2021 study of nine HPC and HPC-related conferences, women represent only 10% of all HPC authors. A 2018 *Wired* article discusses reasons for underrepresentation of women and minorities in technology fields, https://www.wired.com/story/computer-science-graduates-diversity.

national security.<sup>11</sup> Advanced software technologies—including programming models and runtimes, mathematical libraries, data and visualization packages, and development tools that constitute the Extreme-Scale Scientific Software Stack (E4S)<sup>I</sup>—form a community software ecosystem that underpins ECP applications and is unlocking the potential of advanced computing across all scales.<sup>12</sup>

The technical breadth and sustained multilab collaboration of ECP have provided a unique and compelling opportunity for the DOE HPC community to address workforce challenges through a lens that focuses on the distinct needs and culture of DOE HPC, with its emphasis on mission-driven team science.m Consequently, in August 2021 the ECP Broadening Participation Task Force was established, with members representing eight DOE national laboratories—Argonne (ANL), Brookhaven (BNL), Lawrence Berkeley (LBNL), Lawrence Livermore (LLNL), Los Alamos (LANL), Oak Ridge (ORNL), Pacific Northwest (PNNL), and Sandia (SNL)—as well as the DOE Office of Science computing facilities: Argonne Leadership Computing Facility (ALCF), National Energy Research Scientific Computing Center (NERSC), and Oak Ridge Leadership Computing Facility (OLCF). After clarifying the most urgent workforce challenges in the DOE computing sciences and surveying relevant ongoing work, the task force leveraged ECP's unique position as a broad effort spanning the DOE computational research ecosystem to launch the ECP Broadening Participation Initiative.<sup>n</sup> The initiative embodies a collaboration among ECP investigators, facilities staff, and education and workforce professionals. On a path toward a post-ECP role, it has expanded to invite participation from all lab staff in the DOE computing sciences.

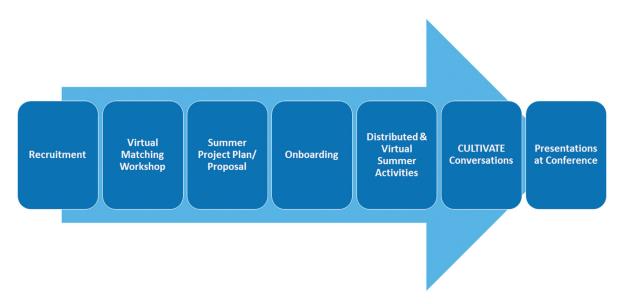

As shown in Figure 1 and discussed in the following sections, the ECP Broadening Participation Initiative features three complementary thrusts: 1) launching the Intro to HPC Bootcamp, an immersive program designed to engage students in energy justice using project-based pedagogy and real-life science stories to teach foundational skills in HPC, scalable AI, and analytics, while exposing students to the excitement of DOE mission-driven team science; 2) expanding the Sustainable Research Pathways (SRP) internship and workforce development program as a multilab cohort of students from underrepresented groups (and faculty working with them), who collaborate with DOE lab staff on world-class R&D projects; and 3) establishing an

**HPC Workforce Pipeline and Career Superhighway**

**FIGURE 1.** The ECP Broadening Participation Initiative supports the full HPC workforce pipeline, from onramps to career retention.

HPC Workforce Development and Retention Action Group to foster a supportive and inclusive culture in DOE labs and communities.

These three thrusts provide paths for student engagement and retention at multiple points of the HPC workforce timeline, increasing access to and enhancing the DOE HPC community. If you imagine the HPC academic and career pathway as a superhighway, as depicted in Figure 1, we envision the three thrusts as onramps at different points, each meeting students (and lab staff) where they are, providing support and preparation, and offering access at appropriate points in an individual's journey. Through these thrusts, the ECP Broadening Participation Initiative supports the full life cycle of the academic and career pipeline.

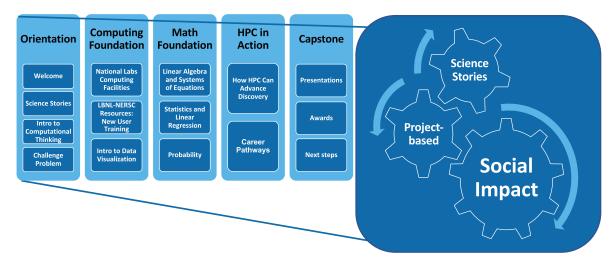

#### INTRODUCTION TO HPC BOOTCAMP

The Introduction to HPC Bootcamp serves as the first entry point onto the HPC career superhighway for students early in their academic careers. The bootcamp is designed to engage students who may not know how or why HPC could help them accomplish their academic and scientific goals, while also preparing them for internships and inspiring them to continue their studies in graduate school.

To this end, the first Intro to HPC Bootcamp° was developed and organized by the advanced computing facilities at ANL, LBNL, and ORNL in collaboration with Sustainable Horizons Institute, taking place in August 2023 at LBNL. The bootcamp brought together 60 students to work in project groups supported by 14 trainers made up of national lab staff and academic partners and 10 peer mentors. Each group of students

https://e4s-project.github.io

<sup>&</sup>quot;R. Giles et al., "Transforming ASCR after ECP," https://science.osti.gov/-/media/ascr/ascac/pdf/meetings/202004/ Transition\_Report\_202004-ASCAC.pdf.

<sup>&</sup>quot;https://www.exascaleproject.org/hpc-workforce

ohttps://shinstitute.org/intro-to-hpc-bootcamp

**FIGURE 2.** The framework of the Intro to HPC Bootcamp focuses on solving problems with mission-driven social impact to engage new communities in HPC.

explored one of seven energy justice projects developed from DOE science that examined issues related to sustainable energy usage and alternatives, social impact of climate risk and resilience, and energy equity in the United States. The bootcamp raised awareness of the power and benefits of HPC, engaging students from historically underrepresented groups in HPC by fostering a sense of belonging and exposing students to opportunities in HPC, especially at DOE labs.

The bootcamp utilized culturally relevant pedagogy and project-based learning to engage students in addressing social impact questions related to energy justice. As shown in Figure 2, the five-day bootcamp began by building community and a friendly learning environment, motivating participants through socially relevant scientific problems, while exposing students to foundational concepts in computing, HPC, mathematics, and analysis. Learners worked throughout the week on their projects, culminating in a presentation on the final day. Throughout the bootcamp, students had opportunities to hear from lab staff about their paths to the national labs and HPC careers.

To ensure an engaging and inclusive bootcamp, we included a diverse set of organizers, trainers, and mentors to develop and facilitate the program. The team had expertise in computational science, advanced computing, energy justice, diversity, education, workforce development, and program evaluation. Collaborators came from multiple DOE labs, Sustainable Horizons Institute, the DOE Office of Economic Impact and Diversity, and academia. Alongside the bootcamp trainers, peer mentors provided guidance on technical concepts, collaboration, workshop expectations, and presentations.

A pivotal step in developing the bootcamp was a Train the Trainers workshop, essential for building effective team collaboration and introducing the bootcamp concept to the DOE lab staff who would serve as materials developers and trainers. During the workshop, the team considered strategies for modifying existing HPC training materials through the lens of engaging new communities and project-based learning.

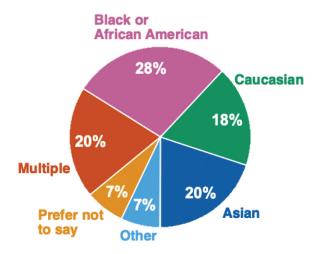

The bootcamp application was designed to lower the barriers for students historically underrepresented in HPC, asking why students wanted to attend the bootcamp without requiring a letter of recommendation or curriculum vita. Of the over 300 students who applied, 60 were chosen to attend; all had some experience with computing but little or no background in HPC. Nearly 80% were undergraduates, along with a mix of master's, Ph.D., and community college students. As shown in Figure 3, the 60 students were diverse racially, with African Americans/Black representing the largest group at 28%, followed by Asian and multiple race (20%) and Caucasian (18%). Nearly all participants (98%) identified as a member of at least one underrepresented group, including 48% first-generation scholars and 57% women participants. For these 60 students, travel, lodging, and food were covered, and a US\$500 stipend was provided at the end of the bootcamp to ensure all students, regardless of financial context, would be able to attend.

Preliminary feedback about the bootcamp has been positive. Of the 54 students who responded to a post-bootcamp survey, 85% said they are interested or very interested in a career in HPC, and 90% said they are interested or very interested in a career at a DOE

**FIGURE 3.** Breakdown of demographics of participants of the Intro to HPC Bootcamp in August 2023.

national lab. In responses to the post-bootcamp survey, many students expressed changes in potential future plans because of their experience at the bootcamp: "[The Intro to HPC Bootcamp] exposed me to work and life at a national lab and motivated me to consider such work...." "If not at a national lab, it has definitely motivated me to look into non-industry jobs that more greatly benefit the public good." "I think I would find that incredibly meaningful and fulfilling, and that is very important to me in a career and something I've been searching for...."

Building on bootcamp successes, we plan to increase access to introductory HPC materials by building in adaptability and customization. Potential paths to increase sustainability and access to the program are through faculty partnerships, asynchronous bootcamp components, providing local offerings, and creating curriculum components to progressively build HPC skills for more advanced learners. By reaching more participants, we are working to build a sustainable pipeline of talent for DOE national labs, preparing students for internship opportunities and providing them with tools to succeed in the next steps of HPC careers.

#### SUSTAINABLE RESEARCH PATHWAYS

Sustainable Research Pathways (SRP)<sup>p</sup> is a comprehensive workforce development program designed to increase the participation of underrepresented groups and institutions in research and development at DOE national labs and to address pressing needs in the advanced scientific computing workforce. SRP serves

as an on-ramp for undergraduate and graduate students with some experience and interest in computing or computational science and engineering. Started as a partnership between Sustainable Horizons Institute and LBNL in 2015,14 SRP expanded beyond LBNL in 2022 as part of the ECP Broadening Participation Initiative. The 2022 SRP cohort was comprised of a highly diverse group of faculty, students of faculty, and independent students who collaborated with staff at 10 DOE national labs on topics involving advanced software technologies and scientific applications. In 2023, the program further expanded through a partnership with ECP and seven labs (ANL, BNL, LBNL, LLNL, LANL, ORNL, SNL) from the Computational Research Leadership Council. During summer 2023, SRP facilitated nearly 200 faculty and student collaborations at 10 DOE labs, and work is underway to prepare for the summer 2024 cohort.

Figure 4 illustrates the program components and timeline. SRP begins with extensive recruitment of faculty, students, and DOE staff members for participation in an interactive virtual SRP Matching Workshop, where participants engage in successively more focused interactions, providing them with the opportunity to explore common interests and potential collaborative summer projects. At the conclusion of the workshop, participants indicate their matching preferences, which are used to create two-way matches (requiring that both parties have expressed interest in working together). Following the matching process, the resulting teams develop brief project plans/proposals for the summer experience, and then funded teams are onboarded at their assigned DOE lab. In addition to pursuing their summer research projects, participants attend local seminars and social events at their host laboratory, as well as virtual cohort-wide SRP activities that help build a multilab SRP community. Volunteer committees provide participants with professional development and leadership opportunities; recent activities have included game nights, wellness events, and seminars on work/life balance. After the summer internship, the Catalyzing Ubiquitous Learning Through InoVaTive and Engaging (CULTIVATE) Conversations program serves to maintain contact with the cohort with the aim of helping develop inclusive workforce ecosystems through facilitated conversations. Participants often showcase their SRP accomplishments at scientific conferences.

SRP faculty alumni accomplishments include DOE Early Career, ASCR-RENEW, and ASCR FAIR awards and nomination for the Presidential Awards for Excellence in Science, Mathematics, and Engineering Mentoring. Student participants have been hired full-time at LBNL, LLNL, and PNNL; decided to pursue graduate

<sup>&</sup>lt;sup>p</sup>https://shinstitute.org/sustainable-research-pathways-2024-workshop

**FIGURE 4.** Components of the SRP program engage students to promote multifaceted learning and community building across a broad timeline before, during, and after the summer internship experience.

degrees; won best poster awards; been awarded the DOE Computational Science and Stockpile Stewardship Graduate Fellowships and Fulbright scholarships; presented their research at prestigious venues such as the Supercomputing and SIAM CSE conferences; and participated in programs such as the Argonne Training Program on Extreme-Scale Computing<sup>q</sup> and the ORNL Artificial Intelligence Workshop.

SRP forms meaningful and lasting connections between faculty, students, and DOE lab staff, while helping to build inclusive HPC research and development ecosystems. Community building activities start at the virtual SRP Matching Workshop and continue during the summer experience and beyond through CULTIVATE Conversations.

#### HPC WORKFORCE DEVELOPMENT AND RETENTION ACTION GROUP

While the Intro to HPC Bootcamp and Sustainable Research Pathways prepare students to enter the HPC career superhighway, we recognize the vital importance of cultivating an inclusive ecosystem, not only to welcome and retain them, but also to foster an environment where they can thrive, meet their potential, and express their full selves. As shown in Figure 1, we complement work to engage students in the HPC workforce pipeline with activities aimed at creating a culture of inclusion. The HPC Workforce Development and Retention (HPC-WDR) Action Group facilitates

collaboration among DOE national laboratories and their associated computing communities to share knowledge and insights aimed at creating a diverse, equitable, and inclusive workforce for HPC. This effort focuses on building a community and gathering proven tools and best practices. Initially, representatives from ten national laboratories convened regularly to exchange ideas and develop recommendations and strategies for building supportive workforce cultures. The first two activities undertaken by HPC-WDR have been organizing a quarterly webinar series on HPC workforce topics<sup>r</sup> and establishing a dedicated website that focuses on fostering a diverse and inclusive HPC workforce culture as well as addressing workforce retention.

The webinars have explored topics such as effective mentoring practices and the significance of embracing diversity for inclusion. Since their inception in May 2022, seven webinars in the series have garnered participation from 672 individuals, representing 10 national laboratories, 38 universities, and 22 businesses, with speakers drawn from the scientific computing community; recordings enable even broader reach.

The HPC-WDR website<sup>s</sup> serves as a repository for webinar recordings and provides announcements of computing workforce events. Moreover, the website houses a growing collection of best practices on HPC workforce issues, often presented in blog posts. For

<sup>&</sup>lt;sup>q</sup>https://extremecomputingtraining.anl.gov

<sup>&</sup>lt;sup>r</sup>https://www.exascaleproject.org/workforce-development-seminar-series

<sup>&</sup>lt;sup>s</sup>https://hpc-workforce-development-and-retention.github.io/hpc-wdr

instance, one blog discusses the adoption of "inclusive minutes" during team meetings.<sup>t</sup> In this practice, teams allocate a minute during their meetings to exchange insights on integrating inclusive and culturally aware practices into their work areas, with a goal of improving communication and fostering mutual respect. Recognizing that changing workplace culture is a complex problem with long timescales, our ongoing objective is to maintain the website as a living community resource and to steward and advance our community's presence. We intend to continue hosting webinars and workforce community meetings, recognizing these activities as vital for assisting the DOE labs' computing community in identifying and implementing best practices in workforce development and retention. Our initial efforts focused on establishing the working group. With a gratifying response from webinar attendees, our next focus is to develop a mixture of qualitative and quantitative methods for capturing impacts and to establish data collection points to measure changes over time, thus motivating further work.

#### FUTURE DIRECTIONS

The ECP Broadening Participation Initiative has established a strong foundation for collaborating and innovating as a multilab community to address challenges in the complete life cycle of the DOE HPC workforce. Early successes include an overwhelming response to the call for participation in the innovative energy justice project-based HPC bootcamp; phenomenal SRP growth from a single lab to a multilab initiative that fostered nearly 200 collaborations across 10 labs in the summer of 2023; and the establishment of a highly collaborative group of laboratory, academic, and industrial HPC professionals who have shared best practices, established a repository of materials, and facilitated webinars attended by nearly 700 people.

The three thrusts—the Intro to HPC Bootcamp, Sustainable Research Pathways, and the HPC Workforce Development and Retention Action Group—provide different entry points onto what we imagine as the fast-paced, exciting, multi-, and interdisciplinary HPC career superhighway. Through this multipronged approach, we can attract students of varied backgrounds, experience levels, and interests, wherever they are in their journeys. We further invite them to join us as we work toward an HPC community where everyone can reach their potential, be their full selves, and contribute to a more innovative mission-driven team science enterprise.

<sup>t</sup>https://hpc-workforce-development-and-retention.github. io/hpc-wdr/jekyll/update/2023/04/08/inclusive-minute.html Together, as we plan for the next phases of work to broaden the participation of underrepresented groups, we are working to realize a sustainable strategy to recruit and retain a diverse HPC workforce by fostering a supportive and inclusive culture within the computing sciences at DOE national laboratories. The exciting and complex era of next-generation computational science demands a multidisciplinary workforce whose members provide a diversity of technical expertise *and* are fully representative of our whole population. This diversity across many axes will inspire innovation, provide new perspectives, and enable us to tackle big problems through HPC team science.

#### **ACKNOWLEDGMENTS**

This work was supported by the Exascale Computing Project (17-SC-20-SC), a collaborative effort of the U.S. Department of Energy, Office of Science, and the National Nuclear Security Administration. We sincerely thank all those who have contributed to the ECP Broadening Participation Initiative for their passion and commitment to advance the DOE workforce in computing sciences. We especially thank members of the ECP Task Force on Broadening Participation, who conceived of and launched the three complementary thrusts; members of the HPC Workforce Development and Retention Action Group, who meet regularly for discussion and actions to advance issues in workforce inclusion; mentors in the Sustainable Research Pathways Program, who host participants from underrepresented groups for summer internships; the team who planned and led the Intro to HPC Bootcamp, including trainers at ALCF, NERSC and OLCF and university partners; members of the Computational Research Leadership Council, who provide support for multilab partnership; ECP leadership; and the DOE Office of Advanced Scientific Computing Research and the National Nuclear Security Administration. This work used resources of the Argonne Leadership Computing Facility, the Oak Ridge Leadership Computing Facility, and the National Energy Research Scientific Computing Center, which are DOE Office of Science User Facilities supported under Contract DE-AC02-06CH11357, Contract DE-AC05-00OR22725, and Contract DE-AC02-05CH11231, respectively.

Notice: This manuscript has been authored by UT-Battelle, LLC, under contract DE-AC05-00OR22725 with the U.S. Department of Energy (DOE). The U.S. government retains and the publisher, by accepting the article for publication, acknowledges that the U.S. government retains a nonexclusive, paid-up, irrevocable, worldwide license to publish or reproduce the published form of

this manuscript, or allow others to do so, for U.S. government purposes. DOE will provide public access to these results of federally sponsored research in accordance with the DOE Public Access Plan (https://www.energy.gov/doe-public-access-plan).

#### **REFERENCES**

- B. Hendrickson et al., "ASCR@40: Highlights and impacts of ASCR's programs," U.S. Department of Energy, Washington, DC, USA, 2020. [Online]. Available: https://www.osti.gov/biblio/1631812

- M. A. Heroux et al., "Basic research needs in the science of scientific software development and use: Investment in software is investment in science," U.S. Department of Energy, Washington, DC, USA, 2023. [Online]. Available: https://www.osti.gov/servlets/purl/ 1846009

- D. Rock and H. Grant, "Why diverse teams are smarter," Harvard Bus. Rev., Nov. 2016. [Online]. Available: https://hbr.org/2016/11/why-diverse-teamsare-smarter

- 4. D. V. Hunt, D. Layton, and S. Prince, "Why diversity matters," McKinsey and Company, Chicago, IL, USA, Tech. Rep., 2015. [Online]. Available: https://www.mckinsey.com/capabilities/people-and-organizational-performance/our-insights/why-diversity-matters

- B. Chapman et al., "DOE advanced scientific advisory committee (ASCAC): Workforce subcommittee letter," U.S. Department of Energy, Washington, DC, USA, 2014. [Online]. Available: https://www.osti.gov/ servlets/purl/1222711

- E. Frachtenberg and R. D. Kaner, "Representation of women in HPC conferences," in *Proc. Int. Conf. High Perform. Comput., Netw., Storage Anal. (SC)*, 2021, pp. 1–14, doi: 10.1145/3458817.3476164.

- T. Whitney and V. Taylor, "Increasing women and underrepresented minorities in computing: The landscape and what you can do," *Computer*, vol. 51, no. 10, pp. 24–31, Oct. 2018, doi: 10.1109/MC.2018. 3971359.

- E. Hammonds, V. Taylor, and R. Hutton, Eds., Transforming Trajectories for Women of Color in Tech. Washington, DC, USA: The National Academies Press, 2022.

- K. Gaither et al., "Advanced computing for social change: Educating and engaging our students to compete in a changing workforce," in Proc. Pract. Experience Adv. Res. Comput. Sustainability, Success Impact (PEARC), Jul. 2017, pp. 1–4, doi: 10.1145/ 3093338.3093391.

- R. K. Raj et al., "High performance computing education: Current challenges and future directions," in Proc. Working Group Rep. Innov. Technol. Comput.

- Sci. Educ. (ITiCSE-WGR), New York, NY, USA: Association for Computing Machinery, 2020, pp. 51–74, doi: 10.1145/3437800.3439203.

- F. Alexander et al., "Exascale applications: Skin in the game," Philos. Trans. Roy. Soc. A, Math., Physical Eng. Sci., vol. 378, no. 2166, Mar. 2020, Art. no. 20190056, doi: 10.1098/rsta.2019.0056.

- L. C. McInnes, M. A. Heroux, E. W. Draeger, A. Siegel, S. Coghlan, and K. Antypas, "How community software ecosystems can unlock the potential of exascale computing," *Nature Comput. Sci.*, vol. 1, no. 2, pp. 92–94, 2021, doi: 10.1038/s43588-021-00033-y.

- M. A. Leung et al., 2023, "Intro to HPC Bootcamp: Engaging new communities through energy justice projects," Figshare, doi: 10.6084/m9.figshare. 24168675.

- 14. M. A. Leung, S. Crivelli, and D. Brown, "Sustainable research pathways: Building connections across communities to diversify the national laboratory workforce," Collaborative Network for Engineering and Computing Diversity (CoNECD), Washington, DC, USA, 2019. [Online]. Available: https://peer.asee.org/sustainable-research-pathways-collaborations-across-communities-to-diversify-the-national-laboratory-workforce

LOIS CURFMAN MCINNES is a senior computational scientist and Argonne Distinguished Fellow at Argonne National Laboratory, Lemont, IL, 60439, USA. Contact her at mcinnes@ anl.gov.

PAIGE KINSLEY is the education outreach lead at the Argonne Leadership Computing Facility, Argonne National Laboratory, Lemont, IL, 60439, USA. Contact her at pkinsley@ anl.gov.

MARY ANN LEUNG is founder and president of Sustainable Horizons Institute, Rancho Mirage, CA, 92270, USA. Contact her at mleung@shinstitute.org.

**DANIEL MARTIN** is a staff scientist in the Applied Numerical Algorithms Group, Lawrence Berkeley Laboratory, Berkeley, CA, 94720, USA. Contact him at dfmartin@lbl.gov.

**SUZANNE PARETE-KOON** is a high-performance computing engineer at Oak Ridge National Laboratory, Oak Ridge, TN, 37831, USA. Contact her at paretekoonst@ornl.gov.

**SREERANJANI (JINI) RAMPRAKASH** is the deputy division director at the Leadership Computing Facility, Argonne National Laboratory, Lemont, IL, 60439, USA. Contact her at ramprakash@anl.gov.

#### **DEPARTMENT: PREDICTIONS**

### Predicting the Future of Supercomputing

Scott Atchley, Oak Ridge National Laboratory

Rosa M. Badia, Barcelona Supercomputing Center

Bronis R. de Supinski, Lawrence Livermore National Laboratory

Joshua Fryman, Intel

Dieter Kranzlmüller, Leibniz Supercomputing Centre

Srilatha Manne , Advanced Micro Devices, Inc.

Pekka Manninen, IT Center for Science

Satoshi Matsuoka , RIKEN

Dejan Milojicic , Hewlett Packard Labs

Galen Shipman , Los Alamos National Laboratory

Eric Van Hensbergen , Arm

Robert W. Wisniewski, Hewlett Packard Enterprise

The need to solve high-complexity problems using large-scale tightly coupled computing (that is, supercomputing) continues to grow. In this article, we address the needs, challenges, and opportunities for supercomputing over the next decade.

upercomputing, which involves the use of the highest-performance computing resources available at a given time, has recently seen broader adoption as it is essential for training generative artificial intelligence/machine learning (AI/ML) models. These AI use cases are in addition to the traditional modeling and simulation (modsim) workloads that continue to drive high use at traditional supercomputing centers.

Supercomputing centers are increasingly adopting Al/ML techniques into modsim workloads. This article by leaders from those centers, as well as within the industry, explores the trends and directions that will shape future supercomputers, driven largely by that convergence of modsim and Al/ML techniques. This article extends the predictions of

several recent articles that explored the future of supercomputing. 1,2,3,4,5,6

#### INCREASING USES, INCREASING ADOPTION

As we consider the future of supercomputing, we see several factors that will drive changes to the work-loads that are run on supercomputers. These changes will continue to broaden the adoption of supercomputing and will affect the technology used to build supercomputers. In this section and the following one, we describe our expectations for future supercomputing workloads and discuss the technologies that will shape their evolution.

While we expect supercomputing workloads to be augmented with new workloads (for example, AI), we expect that traditional supercomputing workloads will remain a significant use case. These traditional workloads serve a wide range of purposes, from advancing science to deepening our understanding of the universe

Digital Object Identifier 10.1109/MC.2025.3567232

Date of current version: 27 June 2025

in which we live, addressing humanity's needs in the modern world, to protecting the national interests of governments that deploy such systems. Nonetheless, we expect these traditional workloads to incorporate new algorithmic techniques, starting with the use of AI/ML models, as has already begun. The adoption of AI/ML techniques includes their use to guide the simulated configurations in ensemble calculations but also their use to accelerate expensive calculations of models of physics and biological phenomena.

With the end of Dennard scaling and the slowing of Moore's law, the automatic increase in performance at constant cost and power is over. Modsim practitioners are faced with modest gains in performance with incremental architecture changes. Future gains are largely coming from the increase in silicon within the package. While providing needed performance boosts, it comes with higher power and higher costs for both the additional silicon and the integration to stitch together several chiplets. When viewed as performance per watt (for example, if a facility has a fixed power budget), then the gains are still modest.

At the same time, the explosive growth in AI, both training and inference, has driven silicon vendors to tailor their products to this lucrative market. It is not clear, however, that modsim can take advantage of lower precision. Some apps will be able to use FP32 for some of their data structures (but not necessarily all) and see benefits compared to lazily promoting everything to FP64. It is not clear if apps will be able to use FP16 for modsim unless it is using AI inferencing in lieu of a component in a multiphysics application, emulation, or iterative refinement. To use ML inferencing, there needs to be an already-trained model. There is a lot of research interest in determining when/if modsim applications can exploit lower precision, which is becoming much more plentiful. There are efforts to see which, if any, apps can use lower precision directly, use lower precision via AI methods, use lower precision via iterative refinement, or use lower precision via emulation. Some apps may be able to do so, while others will not.

The beauty of the General Matrix-Matrix Multiplication (GEMM) emulation methods (that is, Ozaki methods<sup>10</sup>) is that precision is finer-grained than with hardware. Hardware is limited to powers of two (for example, FP64, FP32, and FP16), while Ozaki can provide any multiple of four bits (for example, FP40, FP48, and FP56) to provide just enough precision to converge on a valid solution without providing "too much." While Ozaki's scheme can outperform native cuBLAS in some cases, the downsides to emulation are 1) it can only emulate GEMM (that is, matrix-matrix) instructions but not vector instructions, and 2) it consumes 30-50% of the available memory, thus reducing the solvable problem size. If memory were cheap and plentiful, the latter would not be an issue, but supercomputer users want the fastest memory available. Today, that is high-bandwidth memory, and it is neither cheap nor plentiful. Recently, systems used for AI/ML training have been cast as competitors to supercomputers.

Rather than competitors, the authors view both modsim and AI as having overlapping needs for supercomputer design, except for precision. However, the systems that provide AI/ML capability are best viewed as supercomputers themselves and reflect that AI/ML training has emerged as an important workload for supercomputers. As we look toward the future, not only do we expect that AI/ML training will remain a critical supercomputing workload, but we anticipate that additional new workloads will emerge. We expect that domains that have begun to use supercomputers more extensively due to the success of large-scale AI/ML models, such as finance and retail, will identify new mechanisms to exploit the computational capability available and expand the use of AI/ML in their domain.

The convergence of cloud computing and supercomputing has long been expected. However, this convergence has not fully materialized yet, in part due to the requirements of traditional tightly coupled parallel modsim workloads. Nonetheless, cloud providers continue providing more high performance computing (HPC) capability, and cloud computing continues to be a viable economic and technical alternative for embarrassingly parallel workloads and, as of recently, for AI/ ML workloads. They are also suitable for offloading or bursting small-scale experiments and development.

Addressing humanity's needs, such as weather forecasting and biomedical research, continues to be an important target of supercomputing. These applications include energy needs and its production using nuclear fission near term and fusion long term—but also for fossil fuels and importantly, carbon and water management. Another use is for new materials, particularly for the continued advancement of technology beyond silicon CMOS device scaling. Yet another use case is mitigating and adapting to climate change, including utilizing digital twins.

Digital twins are virtual representations of physical artifacts, systems, or processes with collected real-time information. They enable monitoring, simulation, and prediction of those physical artifacts. Digital twins often use supercomputers directly in a variety of vertical applications and services (for example, for structural analysis, Earth monitoring, manufacturing, and operations) as well as exploit them peripherally (for example, for monitoring, optimizing operation, anomaly detection, or what-if-analysis). Digital twins are used in areas such as the transportation industry, data centers, <sup>11,12</sup> and even Earth. <sup>13</sup>

Another important use case of traditional supercomputing is helping drive new scientific breakthroughs [that is, helping answer the big questions, for example, performing computation for the follow-on to Laser Interferometer, Gravitational-Wave Observatory (LIGO) or Laser Interferometer Space Antenna (LISA) that will enable sensing of gravitational wavelengths populated by a rich diversity in astrophysical phenomena that are of deep interest to astronomers and astrophysicists]. After a discussion on how the use and adoption of supercomputing evolved, we will next explore how technology evolution impacts workloads.

#### EVOLVING TECHNOLOGIES AND WORKLOADS

Future supercomputing workloads will reflect recent and anticipated future technological and industry

developments. These trends include not only the adoption of AI/ML to serve edge computing and other end-user applications but also productivity enhancements, such as those driving broad consumer adoption of cloud-based computing. Further, architectural and device-level advancements will continue to motivate new supercomputing application enhancements. This section provides a high-level description of these two influences on future supercomputers. We begin by describing the workloads.

- New applications are continuing to demand more computational capability, including bioengineering, climate modeling, national security, fusion energy, and many others.

- HPC and AI will continue to converge and thereby demand more AI-ready infrastructure.

- Large language models and other models have captured the public imagination, and they open new opportunities in supercomputing.

- Physics-informed neural networks and other models, possibly integrated into traditional modsim applications, enable the faster exploration of design spaces.

- Some workloads are increasing performance by leveraging mixed precision computation, while others are leveraging multitenancy to increase performance.

- Application demand for scale-up networking, including Ultra Accelerator Link (UALink), will continue to increase per-device bandwidth and the number of directly connected scale-up devices, blurring the boundary between scale-up and scale-out infrastructure.

In the last couple of years, advancements in AI, specifically in generative AI applications, have dramatically influenced private industry toward building large-scale computing infrastructure. Even though these infrastructures are driven by AI requirements, they are becoming increasingly HPC ready. AI and HPC are making significant strides toward convergence, and this development is a major disruptor. We predict the forthcoming technological changes.

Accelerators, from traditional (for example, compression and crypto) to ones focused on

Al (for example, Cerebras, NextSilicon, and SambaNova) to upcoming (for example, neuromorphic and quantum), will address specialized but important demands, and some are already being incorporated into existing supercomputers. 2.5D and 3D memories present obstacles that must be overcome to use, but they provide significant opportunities to help ameliorate memory wall challenges.

- Continued evolution of the scale and latency-sensitive industry-standard or standard-compatible/interoperable interconnects (for example, scale-up merging with scale-out) will occur.

- Increasingly integrated photonics as a means of power reduction, packaging simplicity, and bandwidth enhancement will be seen.

- Improvements in reliability are driven by the need to address resilience (or fault tolerance) at all levels of the system, from hardware to system software to applications.

These technology changes will result in a new macro-political landscape that may influence decisions on next-generation supercomputer procurement. For example

- Al will drive technology directions/priorities, including reduced precision, systolics, and fixed function units.

- Silicon transistor devices are approaching hard limits in scaling, with limited improvements in performance through silicon CMOS scaling, which has implications for specialization, tight integration, and power reduction. These limits introduce a need for deeper co-design alongside other major market forces, such as AI.

- New computing technologies are being explored, including quantum, neuromorphic, and other accelerators that may substantially change the landscape in terms of scaling, reliability, power, and cooling.

- Research in new nonvolatile memories (NVMs) has been occurring for many years. If that work leads to successful productization, it may affect the way we design storage, conduct checkpointing, and in general, manage memory.

New algorithms (potentially AI inspired and enabled by new accelerators) can also impact performance and scale.

#### ARCHITECTURE

Two main architectural changes have brought Al and HPC applications closer together. The first is the addition of high-performance GPUs alongside high-performance CPUs for compute, and the second is Al's need for fast and efficient communication within and between compute elements.

One of the biggest shifts in the last decade has been the widespread adoption of GPUs for computation. While accelerated by AI use cases on supercomputers, this trend was occurring independently on HPC systems due to the need for higher compute capabilities while keeping power manageable. Similar motivators (that is, raw performance, performance per watt, performance per area, and performance per dollar) will likely drive the inclusion of accelerator technology (for example, Cerebras, NextSilicon, SambaNova, and potentially quantum or neuromorphic), though the intercept of the latter two's productive use will require additional time.

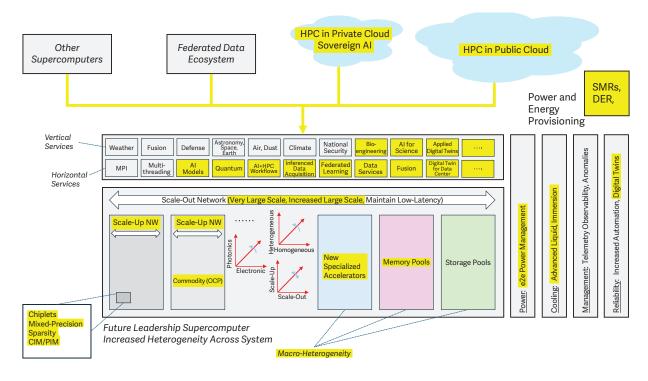

As GPUs became dominant, the primary architecture of the system remained homogeneous by node. That is, while each node was heterogeneous (microheterogeneity), the overall system was homogeneous. Many of these new accelerators are not as general purpose as GPUs, and therefore, systems are likely to be macro-heterogeneous. What remains open is the tightness of coupling of these macro-heterogeneous partitions.

The severity of the memory bottleneck in generative AI has led to other forms of acceleration reentering consideration, including computation near memory (CNM) as well as processing in memory (PIM). These computational accelerators, coupled with collective acceleration in the network, data processing units (DPUs), and forms of compute near storage, create a more diverse acceleration landscape than that enabled by GPUs. Further, as chiplet-based design points lead to finer-grained customization, the opportunity to intermingle compute acceleration with general purpose compute may become attractive to better balance system performance, power delivery, and thermal dissipation.

A major block to heterogeneity, whether it be at the micro or macro level, is the programming model. Without a productive programming model that enables efficient offload to accelerators, the additional hardware will not provide a good return on area, cost, or power investment. The transition from CPUs to GPUs was made easier via a programming model and tool stack for GPUs, and any accelerators will have to match those capabilities to be viable. For example, circuits for CNM have been known for more than 50 years, <sup>14</sup> but the general programmability problem remains unsolved and generally avoided as "too hard" to solve.

One of the significant challenges in the post-exascale era is communication. This challenge involves moving data from memory to compute and between compute. One way to help address this challenge is to move to more tightly coupled architectures. Memory stacking, 2.5D or 3D, has the potential to reduce power and increase bandwidth between compute and memory.

THE FUTURE WILL DETERMINE IF ESS LEADS TO A COMMON STACK ACROSS THE COMMUNITY OR SPLINTERS THE COMMUNITY.

An important aspect of heterogeneous node architectures is moving data between compute elements, specifically between the main CPU and the accelerator. Coarser parallelism leads to less frequent data movement and more efficient use of the accelerator. Traditional HPC applications need serial cores, and many large AI applications are also increasingly benefiting from the utilization of CPUs. Further, many HPC applications remain bulk synchronous with branchy and data-dependent code between parallelizable kernels; that code runs better on CPUs. The AMD Instinct MI300A accelerated processing unit (APU) brings the CPU and the accelerator computing elements together both physically, via chiplets, and programmatically through a unified memory model; Nvidia's Grace-Hopper provides similar benefits using a full reticle CPU and GPU interconnected through NVLink-a chip-to-chip technology. However, hardware and software challenges, such as software offload launch latencies, remain. Tighter coupling may further help improve performance. For example, 3D stacking would allow more memory bandwidth than 2/2.5D integration.

Moving across compute within the same package or same node offers challenges, but significant performance cliffs occur when moving from high-performance nodes to the network due to lower network byte/flop ratios, high network latencies, and high costs of synchronization across nodes. These inefficiencies require application developers to partition their codes in a coarse-grained manner into serial and parallel compute phases, memory movement phases, and network communicator phases with each one optimized independently. This requirement not only impacts programmer productivity but misses opportunities to optimize power efficiency and memory access across the system. These network inefficiencies also limit strong scaling. The bandwidth and latency cliffs are not the only inhibitors of performance. The model of how memory is accessed can also have a large and potentially greater impact on the performance of applications when they communicate outside the node. The right internode memory model with enhanced capabilities, such as atomics and load/store access to memory within a supernode, pod, or hypernode (collections of tightly coupled nodes with an enhanced memory model), can improve strong-scaled performance by more than an order of magnitude. Nvidia's NVLink and the UALink standard (which AMD is a part of) are specific solutions that can provide tighter coupling between nodes. The general UALink industry-standard effort is moving to create an interoperable fabric for these needs. Competing pressures on interconnects will likely move future interconnects from low radix high diameter to high radix low diameter to improve efficiencies across a wide spectrum of use cases.

Two decades ago, the connection model was flat. A core comprised a node, and each node had a network connection. The topology varied (for example, butterfly, hypercube, or torus), but all compute elements were uniformly separated. With the introduction of multiple cores per chip, multiple chips within a node, and multiple GPUs within a node, two levels of connectivity, inter- and intranode, were introduced. This architecture provided a communication latency and

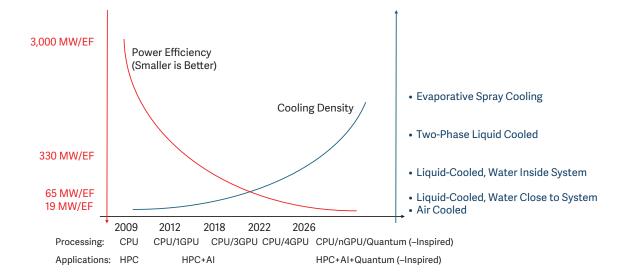

FIGURE 1. Supercomputer power efficiency and cooling over the years.

bandwidth advantage between these computing elements that were contained within a node. However, the architecture came at a cost. Applications—and particularly communication runtimes—needed to be aware of the topological structure to exploit it.

Motivated by AI, scale-up networking is creating another layer in the communication hierarchy. Pods, super nodes, wafer scale, or hypernodes, represent an opportunity to connect tens to hundreds (perhaps small thousands) of nodes in a more tightly coupled manner with memory semantics (for example, load/store access and atomic operations). These architectures have better performance for AI and strong-scaled applications but also introduce a programmability cost. Again, the software layers have an opportunity and responsibility to attune the application appropriately for the communication hierarchy.

An open question remains as to the best overall system architecture since this intermediate communication layer (that is, scale-up: between or within a node and across the whole machine) is more expensive from a cost and power perspective than a flat communication architecture. One possibility that shows promise is merging the connectivity emanating from a node into either scale-up or scale-out connectivity. While this approach is a promising notion, no obvious technologies enable it, yet, but the two main standards initiatives in this space, UALink and the Ultra-Ethernet Consortium (UEC), are currently working on it.

Traditionally, the HPC community relied on large-scale hard-drive-based parallel file systems, such as Lustre and GPFS. In recent times, object store file systems optimized for NVM technology, such as DAOS, VAST, and Weka, are gaining popularity and will increase, including the model stores for AI, such as vector databases. Cloud services have innovated object interfaces, such as S3, that AI frameworks use natively.

#### **FACILITIES**

Energy has been driving exascale supercomputing as one of the primary constraints. From the beginning of exascale planning, the desire to keep the spending on power to a minimum led to a target of 20 MW. 15,16 This impacted system designs, specifically cooling, space (the number of racks), and the CPU/GPU ratio. Air cooling was not sufficient, and liquid cooling has become the standard solution for capability-class supercomputers and is seeing broader-based adoption.

Figure 1 notionally presents the evolution of power efficiency on the left (red curve) versus cooling choices on the right (blue curve) during the past few decades. Power efficiency numbers were taken from Oak Ridge National Laboratory supercomputers (Jaguar, Titan, Summit, Frontier). Due to 3D chips, the power density will continue to increase (more than double from 2021 to 2031) according to the IRDS Roadmap, which will require further innovation in cooling, such as immersive or evaporative spray cooling.

In the longer term, both cooling and power requirements may change substantially. Multiple reasons led to the 20-MW limit in the requirements for exascale supercomputers, including cost and the ability to deliver that much power. The new means of energy production, such as small modular reactors (SMRs), are competitively priced per MW and complemented by onsite renewable energy production (for example, wind and solar). If they succeed, they will address both the cost and power delivery to data centers. The Al compute demand and the boom have further shifted the economics and scale of power generation, altering availability and pricing.

#### SOFTWARE STACK

The system software stack, as defined by everything below an application and above the hardware, continues to increase in complexity. From a modeling and simulation perspective, as the desired capability has increased, system implementers have increasingly turned toward leveraging open source to provide this capability. This change complicates comprehensive testing. The combinations of open source components exponentially increase the number of possible permutations of the software stack. Insufficient connectivity between these open communities (and interest in being connected) has made comprehensive validation significantly more challenging than when a vendor owned all, or most of, the components in a stack.

OpenHPC created a complete and comprehensive system general software stack. Extreme-scale Scientific Software Stack (E4S) of the Exascale Computing Project (ECP) made strides toward unifying the development environment across many open source components. The High Performance Software Foundation (HPSF), unified by Spack, is making strides toward providing optimized software stacks for well-defined systems. Nonetheless, challenges remain, and a stronger community testing effort, perhaps under HPSF, is still needed.

The inclusion of AI software stacks on supercomputers has significantly increased the number of components of the overall software stack. More importantly, AI infrastructure, including the software stack, is undergoing rapid change. The key contributors are investing significant effort to support this rapidly evolving environment while other organizations are challenged to keep up. Overall, the rapid evolution limits the organizations that can stand up and maintain an AI stack, which further increases the need for community efforts toward testing and maintaining the overall software stack.

While E4S was United States centered, Europe is developing the European Software Stack (ESS). The EuroHPC JU will work with stakeholders to coordinate co-design in the research and investigation of hardware and software activities and ensure that those activities meet user requirements and that developed technologies are deployed. Funding is planned for the different building blocks in HPC, AI, and quantum computing (QC) from innovation to deployment, targeting different technical readiness levels as required by the status of hardware developments. Europe will focus on multiple aspects, such as performance and efficiency, Al-software integration, energy consumption, workflow managers, and support to European processors, among others. The future will determine if ESS leads to a common stack across the community or splinters the community.