# TDD For Embedded Systems... All The Way Down To The Hardware

Neil Johnson

XtremeEDA

njohnson@xtreme-eda.com

@nosnhojn

## What Do I Mean By Hardware

#### ASIC

- Application Specific Integrated Circuit

- Static structure

- Digital or mixed signal

- High NRE/Low cost

#### FPGA

- Field Programmable Gate Array

- Reprogrammable structure

- Primarily digital

- No NRE/High cost

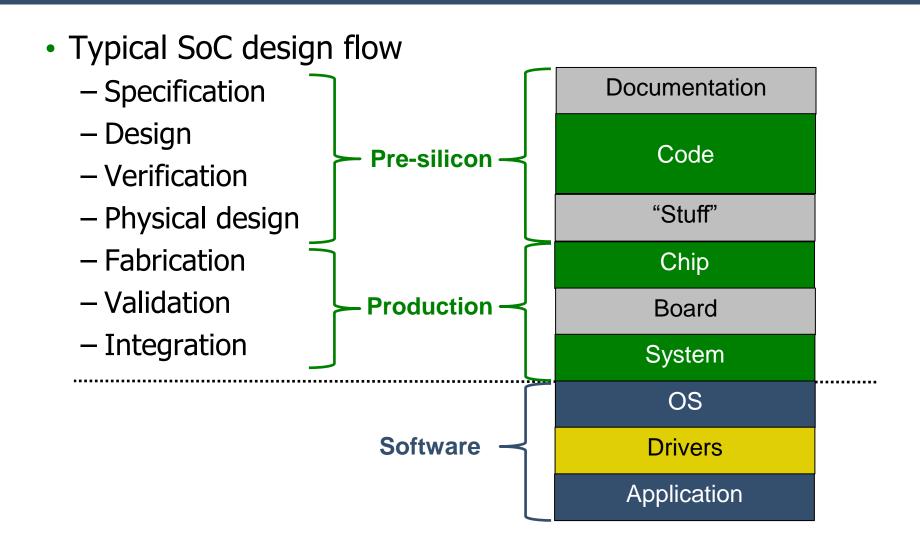

#### SoC

- Either of the above + embedded processor(s) + software

#### **SoC Development Basics**

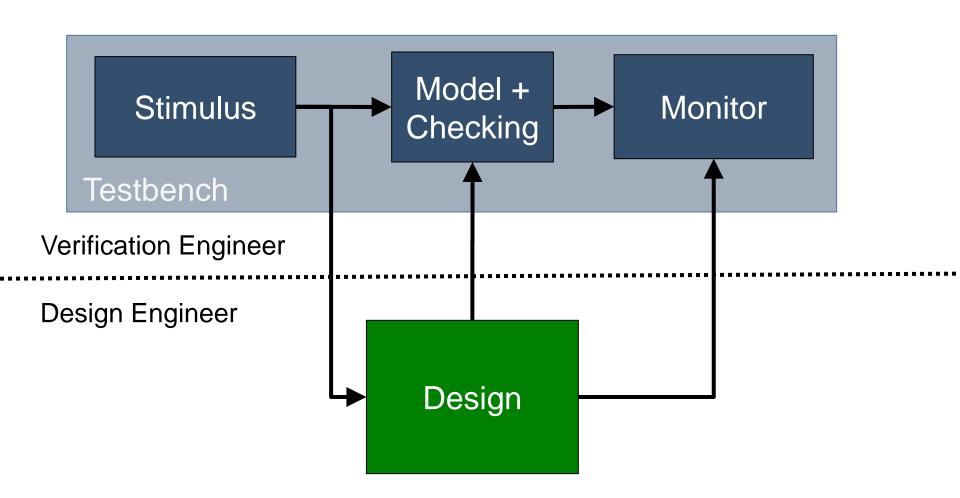

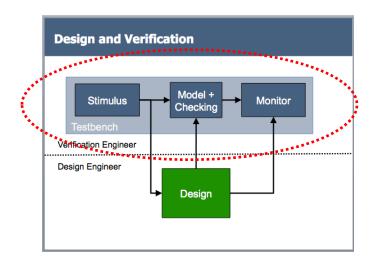

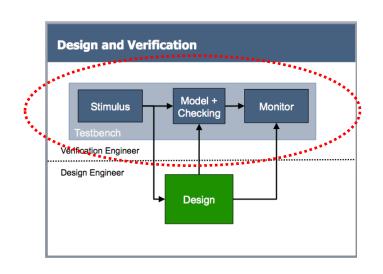

# **Design and Verification**

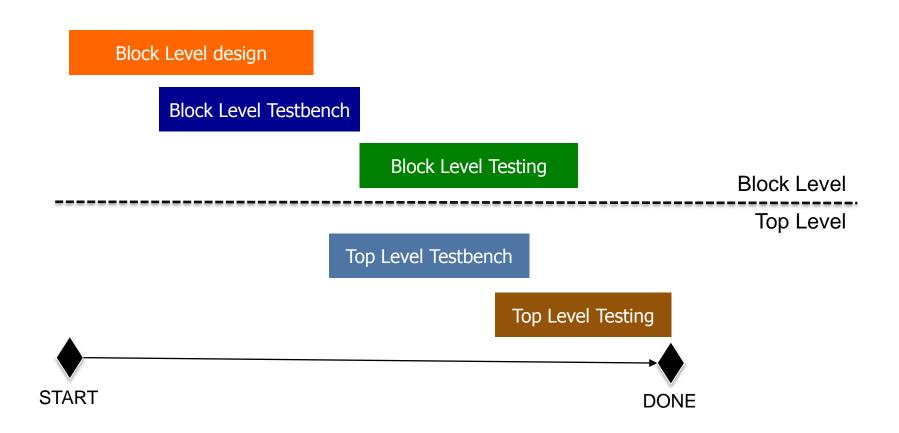

## **Design and Verification – Planned?**

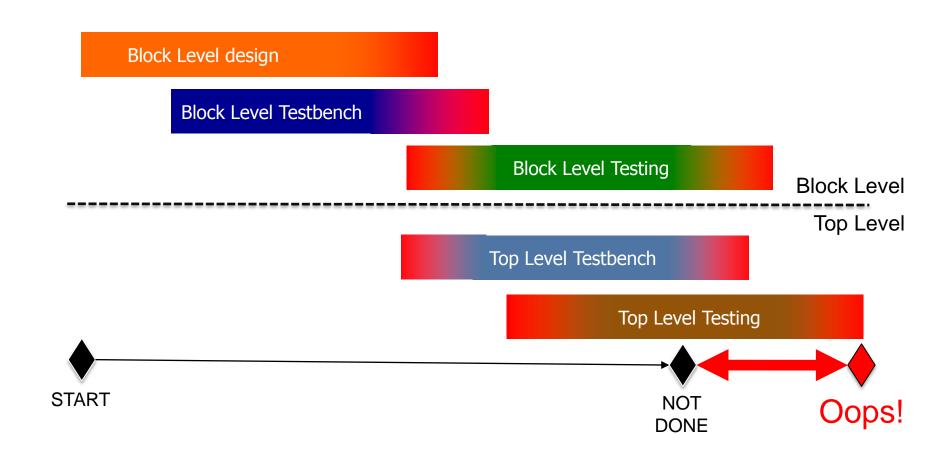

## **Design and Verification – Actual!**

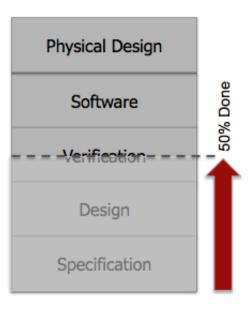

## **Working Software (Hardware)**

#### **Working Software (Hardware)**

Waterfall Model

Agile model

© 2011 XtremeEDA USA Corporation - Version 080721.10

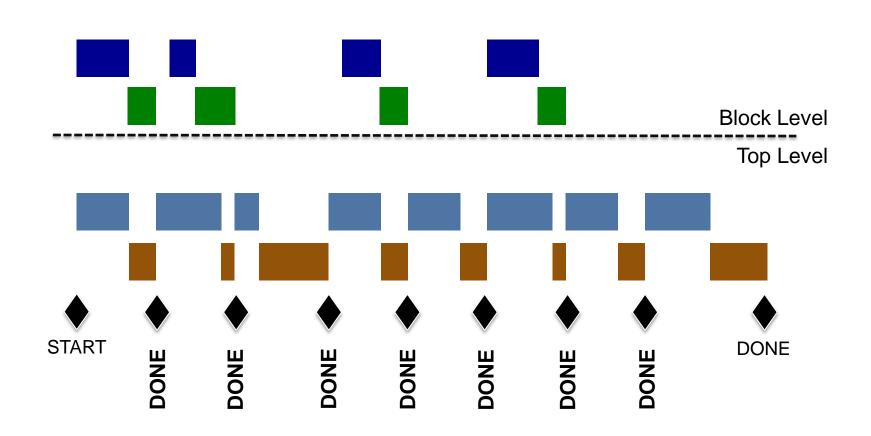

## **Design and Verification – Incremental**

#### **The Perfect Place To Start**

- Feature-of-the-week

- "Tell your customer you're going to give them something that works in a week"

- Jonathan Rassmuson, Agile in a Nutshell, APLN April 2009

- The Agilesoc Blog: Remote Development And The Featureof-the-week

The feature-of-the-week is not Agile, it's frequent delivery... which is hard to argue against.

- Client experience

- Goal

- Convince myself that incremental development is possible

- Situation

- Functional testing of a sub-system

- Design was done, test harness was partially complete

- Planning

- 4 increments, 1 for each major feature

- Detailed plan included 1-2 week sub-milestones

- 2 increments planned in detail

- Client experience Highlights

- Planning

- The planning was different but no convincing was required

- Increment 1

- Uh oh... I've committed to delivering something in a week

- First up: remove everything I don't need

- Client experience Highlights (con't)

- Increment 2

- I was focused and delivering on time

- Functional milestones allowed me to react to new priorities

- Increment 3

- Functioning code was great for gaining confidence and/or being corrected

- I wasn't so concerned with building infrastructure

- Client experience Highlights (con't)

- Increment 2

- I was focused and delivering on time

- Functional milestones allowed me to react to new priorities

- Increment 3

- Functioning code was great for gaining confidence and/or being corrected

- I wasn't so concerned with building infrastructure

- Summary

- Convince myself incremental development can work

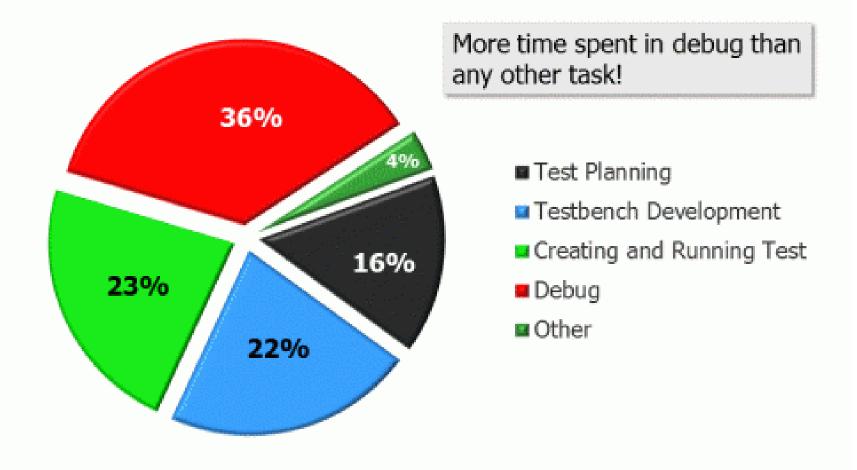

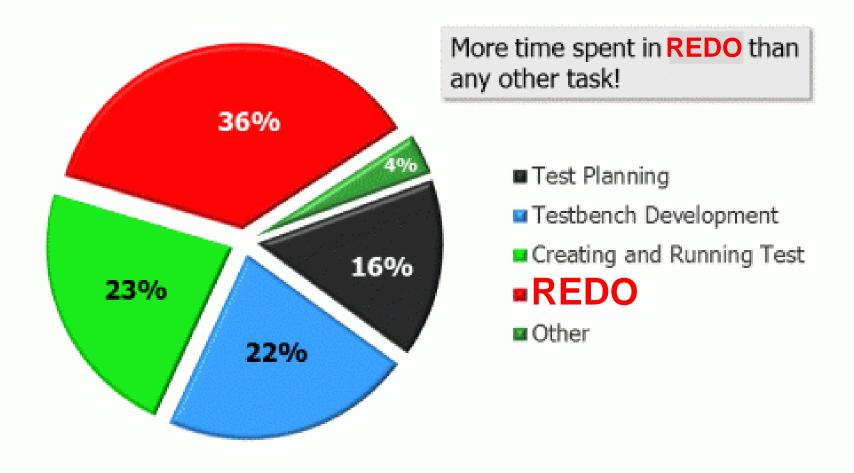

#### **Effort and Results**

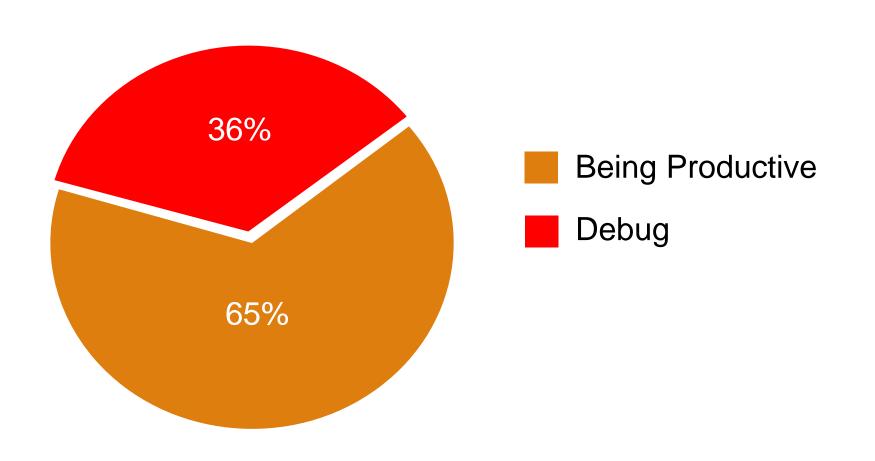

Mean time Non-FPGA verification engineers spends in different tasks

Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study, Used with permission

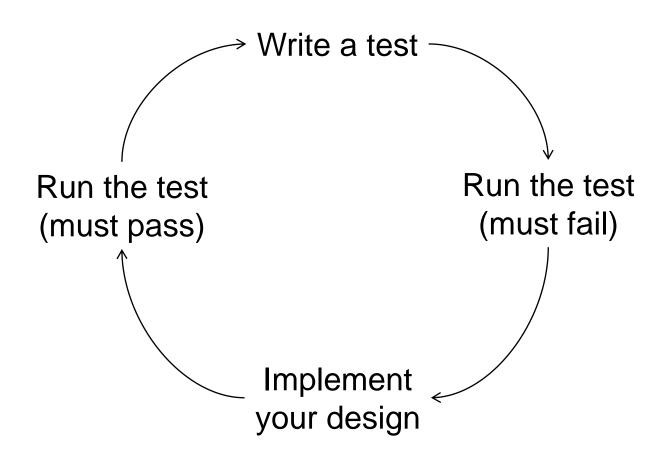

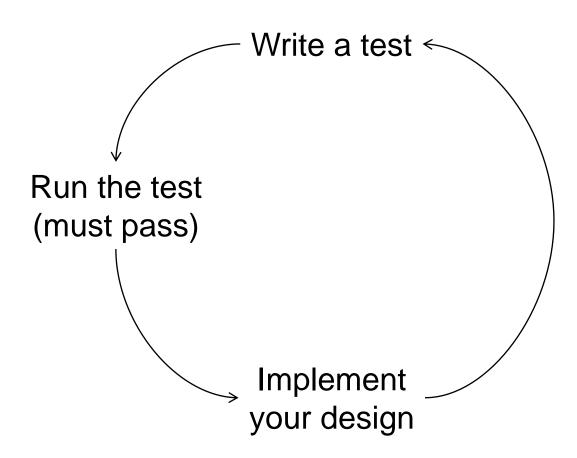

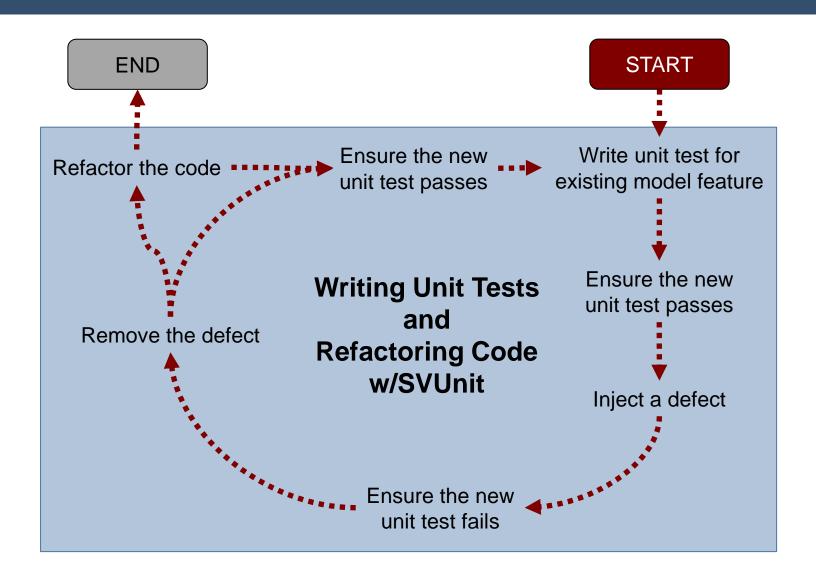

#### **TDD Mechanics**

# **Unit Testing Mechanics**

## **TDD To Improve Initial Code Quality**

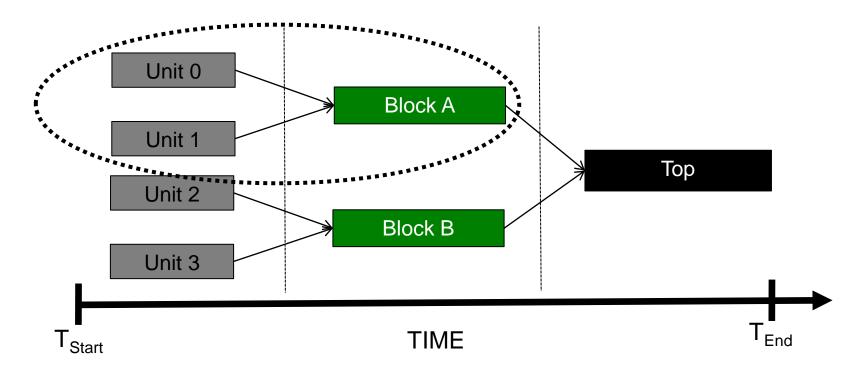

- Each module in a design has a list of dedicated unit tests

- tests exhaustively cover functionality of the module ("exhaustively" within reason)

- unit tests are automated

- anytime the code changes for a given module, the corresponding tests are run to make sure it isn't broken

- Unit tests informally increase quality, not red tape

- tests are planned/written while building a component

- documentation/tracking requirements are very light

- "Use-this" modules are integrated when their unit tests pass

## TDD To Improve Initial Code Quality

- Unit testing happens before anything else

- then block and/or top level testing

- Unit testing does not replace current verification practices

- change... perhaps. replace... no.

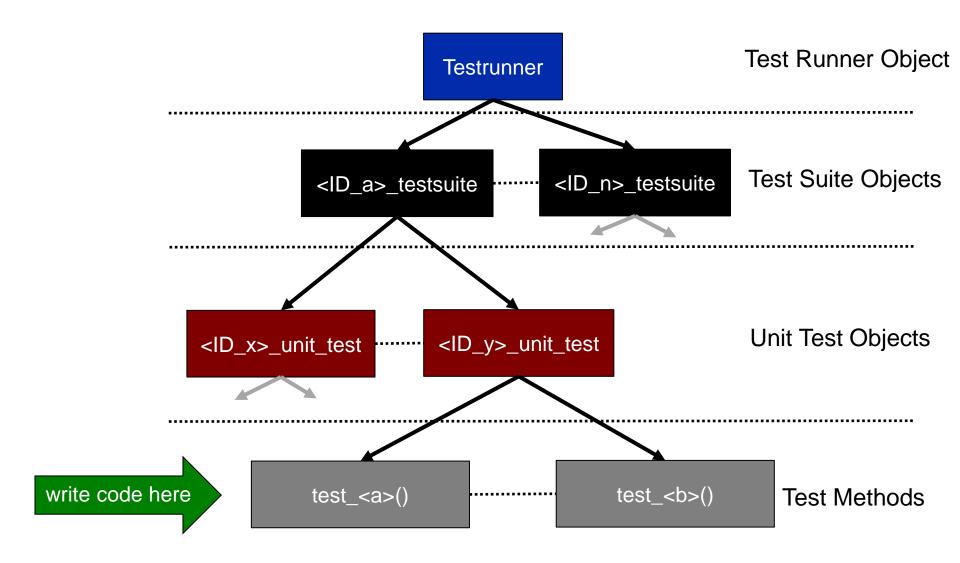

## **SVUnit Testing Framework**

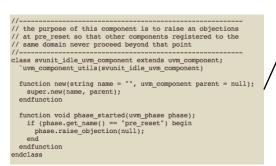

#### **SVUnit In Practice - Mechanics**

#### **SVUnit In Practice - Mechanics**

#### **SVUnit In Practice - Mechanics**

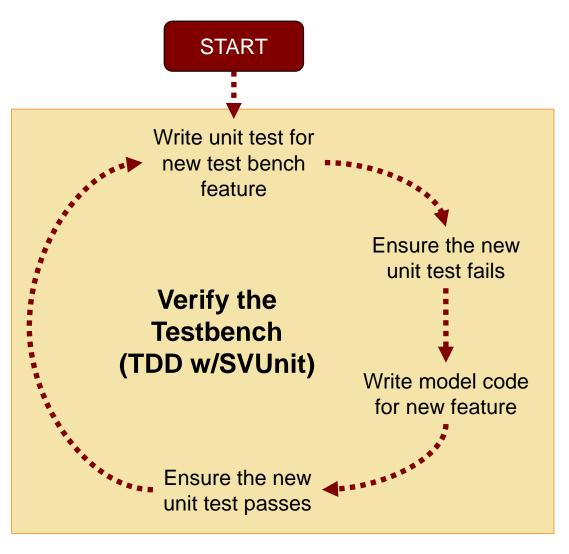

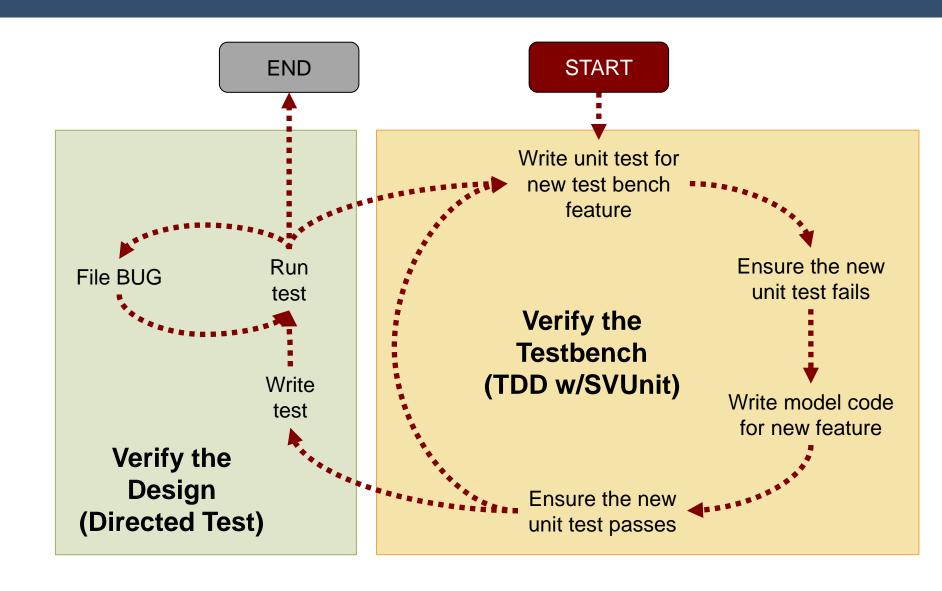

## **TDD To Improve Initial Code Quality**

- TDD for Testbench Code

- UVM testbench for SoC subsystem

- ~3000 lines of code total

- SVUnit unit tests for almost every line

- 116 unit tests

- ~5000 lines of test code total

## **TDD To Improve Initial Code Quality**

- TDD for Testbench Code

- UVM testbench for SoC subsystem

- ~3000 lines of code total

- SVUnit unit tests for almost every line

- 116 unit tests

- ~5000 lines of test code total

- -9 weeks of effort

- Bugs found:

- 30 RTL bugs

- 2 testbench bugs

## **Design Lessons Learned**

- Can TDD be effective given low level interactions?

- Is code partitioning TDD-friendly?

- Can concurrency be hidden/simplified?

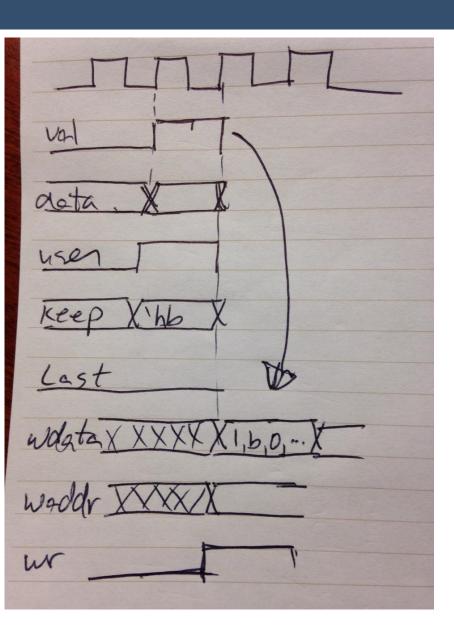

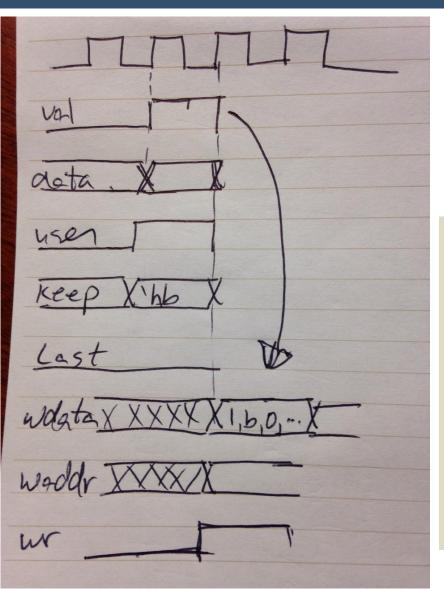

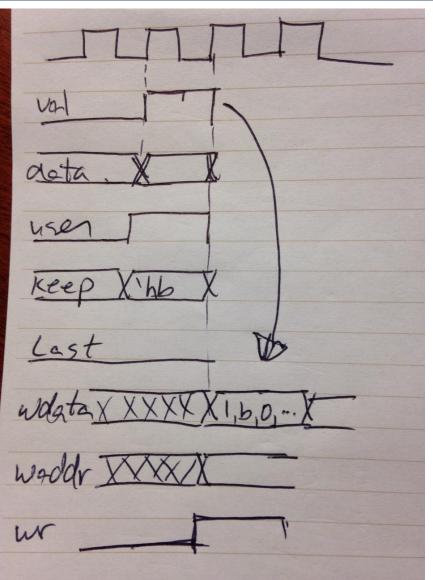

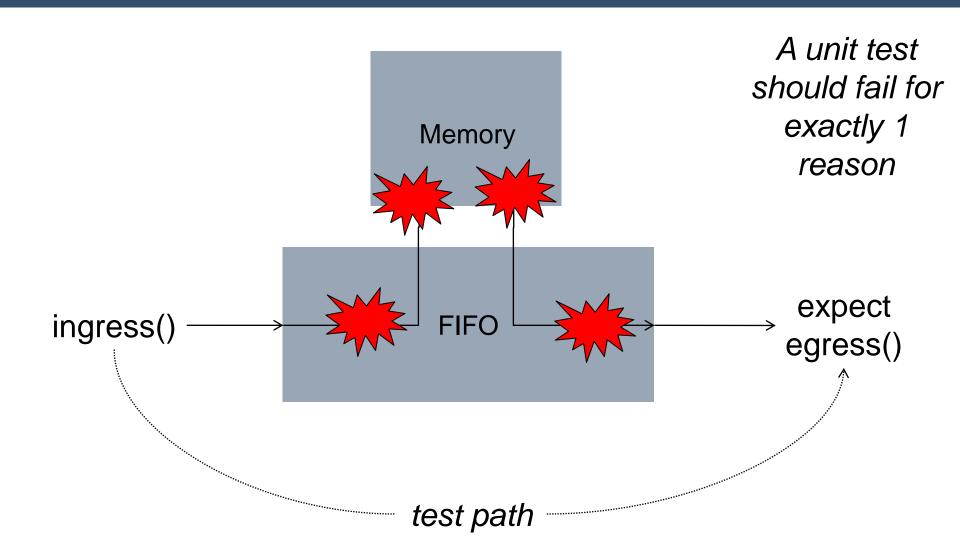

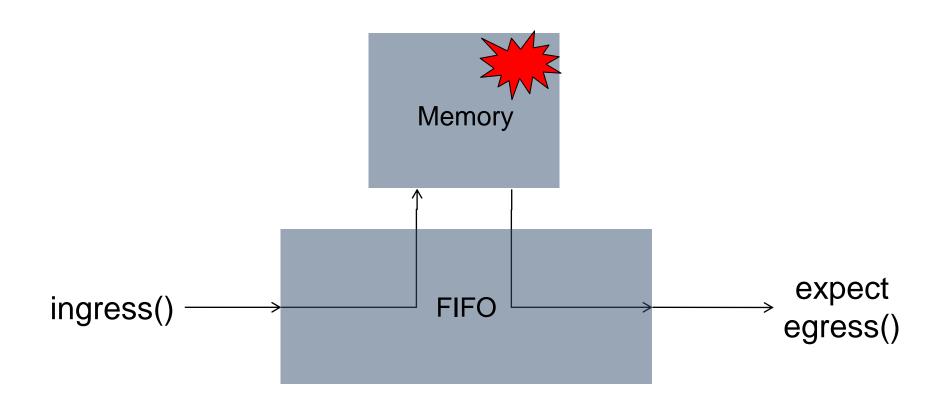

#### **Problem: Low Level Hardware Interactions**

#### **Problem: Low Level Hardware Interactions**

```

`SVTEST(ingress_write_1_pixel)

@(posedge clk);

iTVALID = 1;

iTDATA = 'haa55bb;

iTUSER = 1;

iTKEEP = 'hb;

iTLAST = 0;

@(posedge clk);

#1;

`FAIL_UNLESS(wdata === { 1 , 'hb , 0 , 'haa55bb });

`FAIL_UNLESS(waddr == 0);

`FAIL_UNLESS(wr === 1);

`SVTEST_END

```

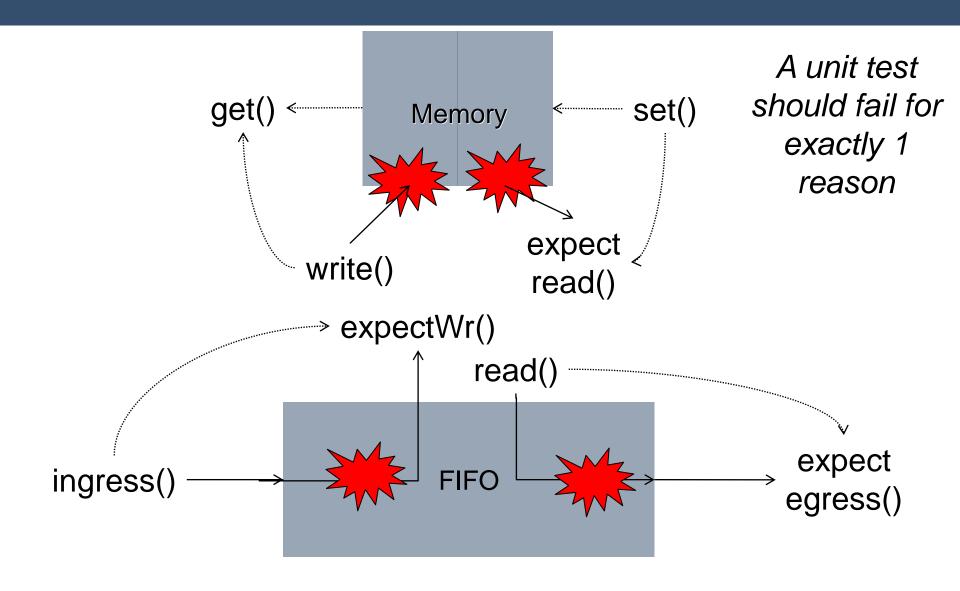

#### **Solution: Create Higher Level API**

```

SVTEST(ingress_write_1_pixel)

setIngressPixel('haa55bb);

step();

expectRamWrite(0, 'haa55bb);

SVTEST_END

```

```

SVTEST(ingress_write_1_pixel)

@(posedge clk);

iTVALID = 1;

iTDATA = 'haa55bb;

iTUSER = 1;

iTKEEP = 'hb;

iTLAST = 0;

@(posedge clk);

#1;

FAIL_UNLESS(wdata === { 1 , 'hb , 0 , 'haa55bb });

FAIL_UNLESS(waddr == 0);

FAIL_UNLESS(wr === 1);

SVTEST_END

```

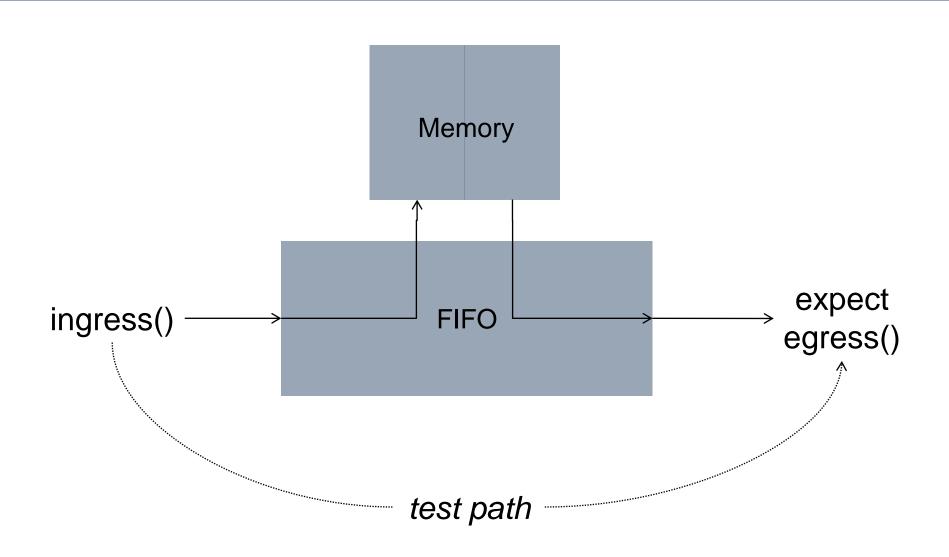

## **Problem: Not Structured for Unit Testing**

#### **Problem: Not Structured for Unit Testing**

## **Solution: Restructure/Isolate Functionality**

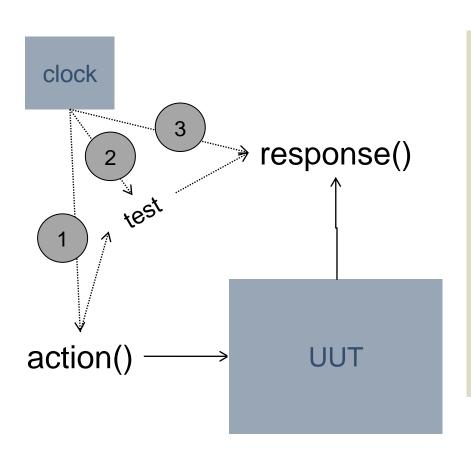

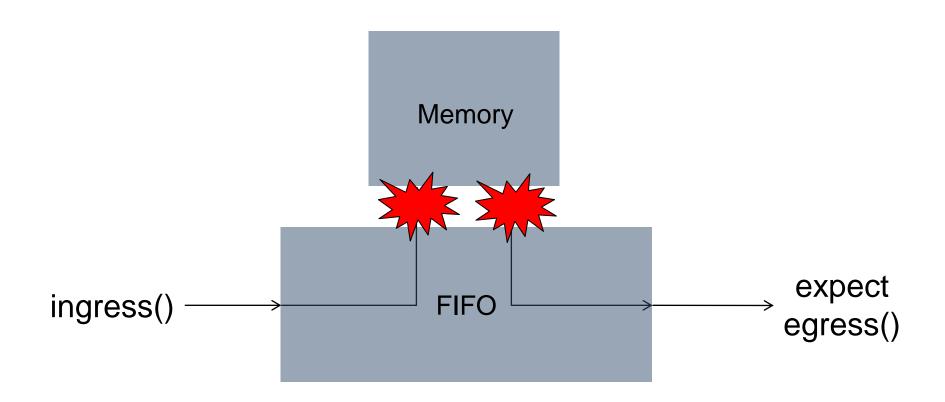

#### **Problem: Hardware is Multi-Threaded**

```

`SVTEST(test with 3 threads)

// syncronize to clk thread

@(negedge clk);

fork

begin

// some action on input thread

end

begin

// wait for response thread

`FAIL IF(someCondition);

end

join

SVTEST END

```

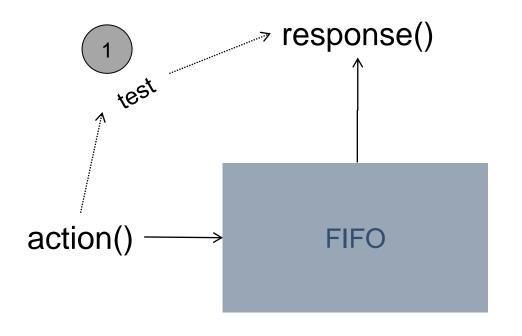

#### **Solution: Maintain a Single Thread**

```

`SVTEST(ingress_write_1_pixel)

setIngressPixel('haa55bb);

step();

expectRamWrite(0, 'haa55bb);

`SVTEST_END

```

## **Design Lessons Learned**

- Low level interactions can work with TDD

- Design partitioning can be TDD-friendly

- Concurrency can be hidden/simplified in unit tests

- Hardware is special... but TDD still fits

Where would I be without TDD and incremental development?

Mark Villalpundo

Sponsored by: 061 Marin harding

E Xtreme EDA

RealityReused.com

## **SVUnit Case Study: UVM-UTest**

- Unit testing legacy code: UVM-1.1d

- Lock down functionality to ease maintenance

- finer granularity tests catch issues we don't target directly

- unit tests provide a backstop when maintaining code

- UVM-1.1d == thousands and thousands of lines of code

- >550 unit tests total

- 6 weeks of effort

#### **SVUnit Case Study: UVM-UTest**

- Unit testing legacy code: UVM-1.1d

- Lock down functionality to ease maintenance

- finer granularity tests catch issues we don't target directly

- unit tests provide a backstop when maintaining code

- UVM-1.1d == thousands and thousands of lines of code

- >550 unit tests total

- 6 weeks of effort

- 10 defect reports filed

| Viewing Issues (1 - 10 / 10) [ Print Reports ] [ CSV Export ] |          |           |             |          |          |               |                  |                                                                                                           |

|---------------------------------------------------------------|----------|-----------|-------------|----------|----------|---------------|------------------|-----------------------------------------------------------------------------------------------------------|

|                                                               | <u>P</u> | <u>ID</u> | <u>Type</u> | Category | Severity | <u>Status</u> | <u>Updated</u> ▼ | Summary                                                                                                   |

|                                                               |          | 0004602   | TBD         | BCL      | minor    | new           | 2013-06-19       | uvm_printer::print_object_header cannot support user specified scope_separator                            |

|                                                               |          | 0004600   | TBD         | BCL      | minor    | new           | 2013-06-19       | incomplete string/separator handling in uvm_leaf_scope                                                    |

|                                                               |          | 0004640   | TBD         | BCL      | minor    | new           | 2013-06-17       | $\mbox{uvm\_has\_wildcard}$ is the only function that treats '+' as wildcard                              |

|                                                               |          | 0004638   | TBD         | BCL      | minor    | new           | 2013-06-17       | uvm_is_array returns true for malformed string inputs                                                     |

|                                                               |          | 0004637   | TBD         | BCL      | minor    | new           | 2013-06-17       | incomplete is_wildcard handling in<br>uvm_get_array_index_string leaves is_wildcard in<br>erroneous state |

|                                                               |          | 0004636   | TBD         | BCL      | minor    | new           | 2013-06-17       | uvm_get_array_index_string accepts illegal index characters                                               |

|                                                               |          | 0004635   | TBD         | BCL      | minor    | new           | 2013-06-17       | incomplete is_wildcard handling in uvm_get_array_index_int leaves is_wildcard in erroneoustate            |

|                                                               |          | 0004634   | TBD         | BCL      | minor    | new           | 2013-06-17       | uvm_get_array_index_int treats indices with radix specified as illegal                                    |

|                                                               |          | 0004609   | TBD         | BCL      | minor    | new           | 2013-05-28       | uvm_printer::print_real argument to adjust_name is incorrect                                              |

|                                                               |          | 0004601   | TBD         | BCL      | minor    | new           | 2013-05-24       | uvm_vector_to_string incorrectly displays negative numbers                                                |

|                                                               |          |           |             |          |          |               |                  |                                                                                                           |

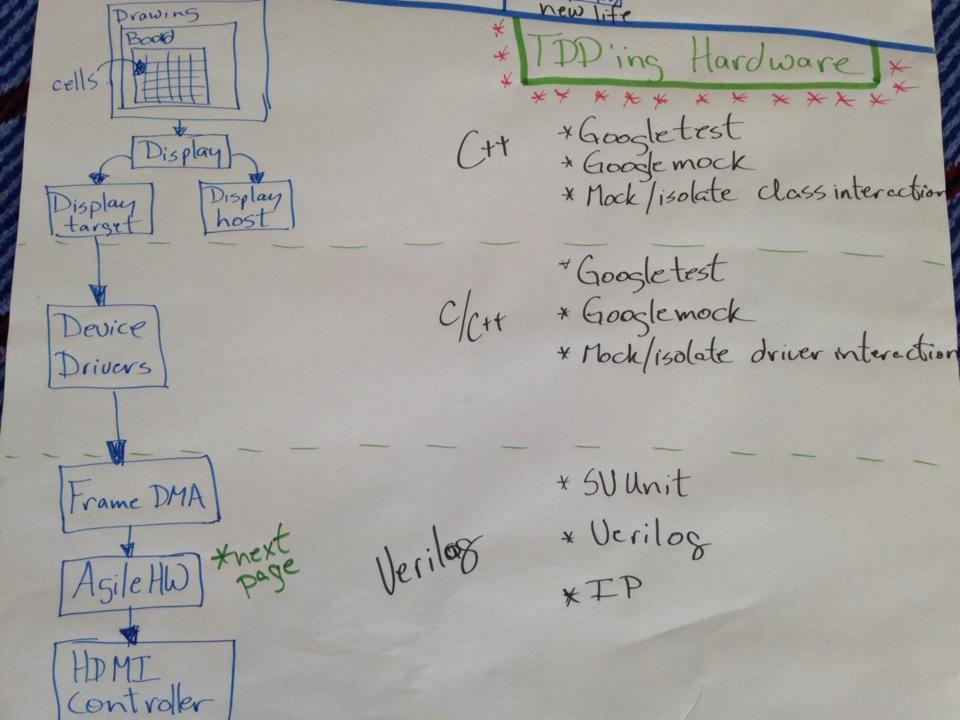

### **SVUnit Case Study: UVM-UTest**

My Commitment to Agile Hardware development is to ... Build a platform to showcase TDD as a credible technique This is why I'm making this commitment. code quality and synchronization between huge developers are of major importance in embedded systems development. I think this platform could be a great tool for activesing both issues; for doing hw/sw co-denelopment. TOD being applied in both domains on a platform that This is how I intende to meet my commitment. We'll use and an FPGA board to implement some simple yet visual application. The app will be golit between 50 running on an ARM Cortex As and logic on the fpga well build the code on both sides with likely Gogsletest for the C/C++ and State suunit on the verilage side. For people that use the platform, they'll have access to all the cake so they can add/change/move features in or between sw/hwdomains. then they can rebuild Iduplay and watchit go. Ease of use is top priority we want people to be countertable playing whit. This is how I'll know if I've achieved my Comm. tmnt ... I'll take it 6 Agile 20H and set it up in the coachie ocea. If I get 10 people sitting down, changing code, rebuild and redeploy then I'm happy less than 10 will be a miserable failure! I plan to meet my Commtment by... Agile 2014 conference is July 28th Done and polished before PS: "We" is me and Soheil. This Apr 10/2014. Solil Salchien April 16/2014

"...showcase TDD as a credible technique for doing hw/sw co-development."

"code quality and synchronization between hw/sw developers are of major importance in embedded systems development."

"we'll use an FPGA board to implement some simple yet visual application."

gile Soc.com Agile Hardware w/TDD Application Programming Steps ARM < 2 neighbours Program underpopulated 2113 neighbour Run SW ARM sustained ARM >4 neighbours over populated 3 neighbours Drawing

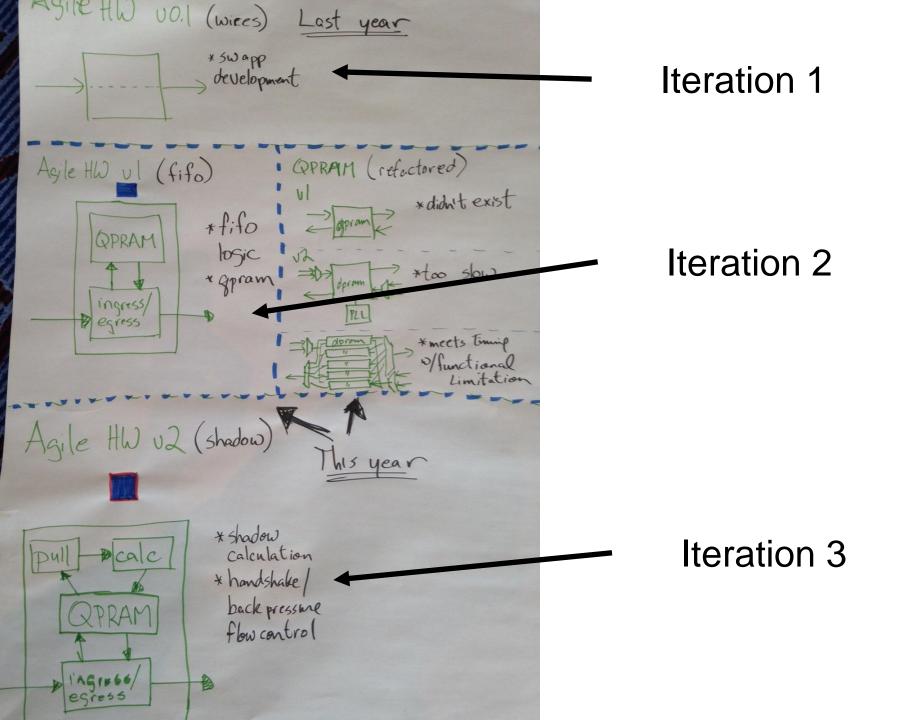

## **Problem: Design Doesn't Meet Timing**

QPRAM (refactored) \*didn't exist \*meets Timip W/functional Limitation

## **Problem: It's Not Over With TDD**

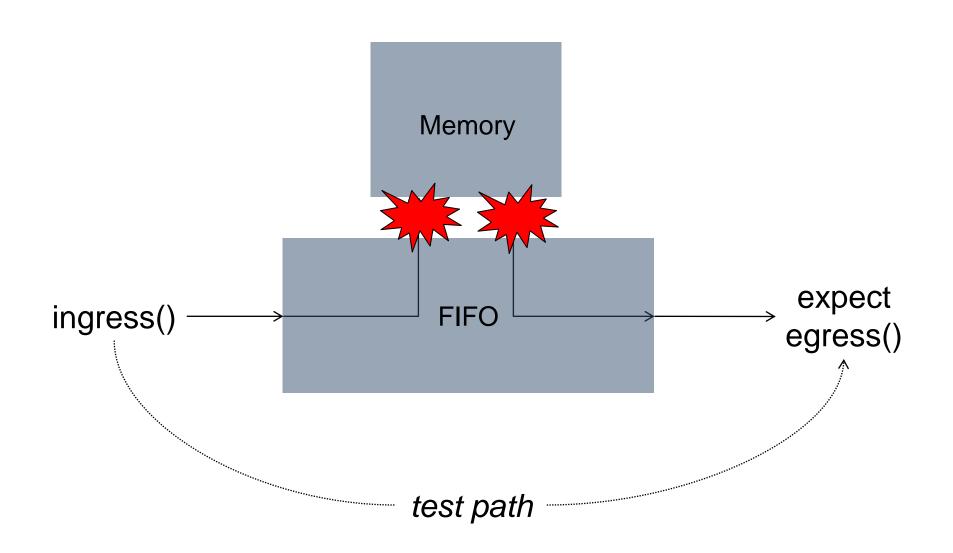

# **Solution: Integration Tests For Integration**

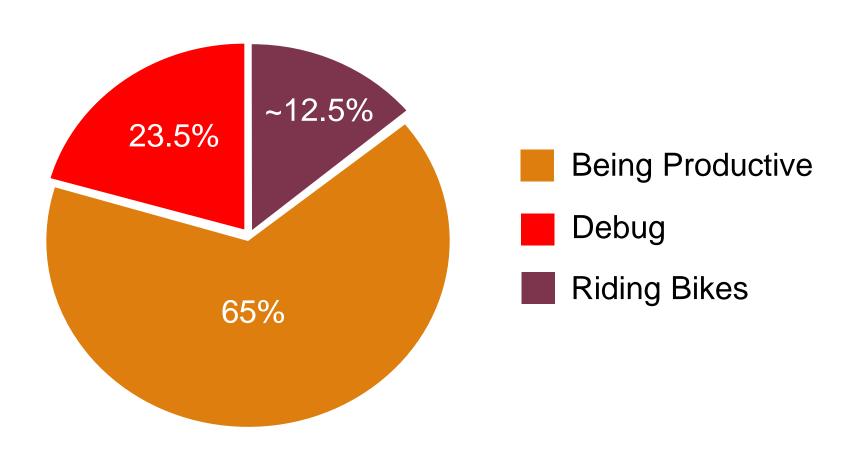

## Where Verification Engineers Spend There Time

## Where Verification Engineers Spend There Time

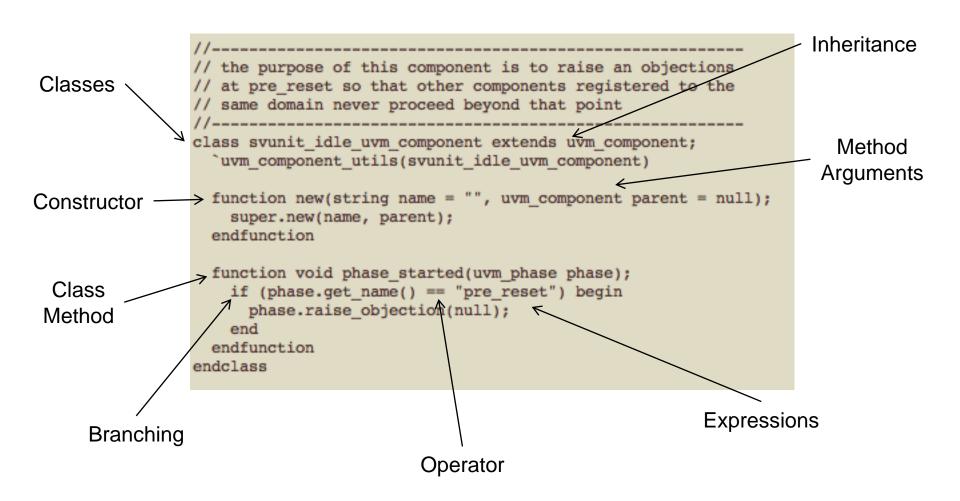

## Language Basics (Verification)

## Language Basics (Design)

```

// calculate the waddr to the memory based on the

// frame position flags

//----

Synchronous

Logic

always @(negedge rst n or posedge clk) begin

if (!rst n) begin

next waddr <= 0; ←

Reset State

end

else begin

Flip-flop

if (calc strobe && first row flag && first column flag) begin

next waddr <= EFFECTIVE WIDTH;

end

else if (calc strobe && last row flag && first column flag) begin

AND/OR gates

next waddr <= next waddr + EFFECTIVE WIDTH;

end

else if (calc strobe && first row flag && !first column flag | | 4

calc strobe && last row flag && !first column flag

strobe 3 of 4) begin

next waddr <= next waddr - EFFECTIVE WIDTH;

end

else if (strobe 2 of 2 | strobe 2 of 4 | strobe 4 of 4) begin

next waddr <= next waddr + EFFECTIVE WIDTH + 1;

end

else if (next wr) begin

if (next waddr < 6 * EFFECTIVE WIDTH-1) next waddr <= next_waddr + 1;

Adder

next waddr <= 0;

else

end

end

end

```

#### **Hardware Simulation**

Simulator

results.log

#### **Effort and Results**

Mean time Non-FPGA verification engineers spends in different tasks

Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study. Used with permission

TDD is a great idea that can save us a lot of money by helping us avoid writing buggy code.